# Video Display Processors

Programmer's Guide

Video Display Products

# Video Display Processors

Programmer's Guide

Texas Instruments Semicondo in Products P.O. Box 309066 Dallas, Toxas 75380-9066

Texas Instruments

#### **IMPORTANT NOTICE**

Texas Instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

Texas Instruments assumes no responsibility for infringement of patents or rights of others based on Texas Instruments applications assistance or product specifications, since TI does not possess full access to data concerning the use or applications of customer's products. TI also assumes no responsibility for customer product designs.

Copyright © 1984, Texas Instruments Incorporated

# **CONTENTS**

| SECTION |      |         | TITLE                                        | PAGE |

|---------|------|---------|----------------------------------------------|------|

| 1.      | 1.1  | Genera  | ION                                          | 1-1  |

|         | 1.2  | Referer | nce Material                                 | 1-2  |

| 2.      |      | URES    |                                              | 2-1  |

|         | 2.1  | Display | / Planes                                     | 2-1  |

|         | 2.2  |         | / Modes                                      |      |

|         | 2.3  | Availab | ole Colors                                   | 2-3  |

| 3.      | СОМ  | MUNICA  | ATION BREAKDOWN                              | 3-1  |

|         | 3.1  | CPU to  | VDP Interface                                | 3-2  |

|         | 3.2  | Softwa  | are Operations                               | 3-2  |

| 4.      | TALK | ING TO  | THE VDP                                      | 4-1  |

|         | 4.1  |         | to the VDP Registers                         |      |

|         | 4.2  |         | g the VDP Status Register                    |      |

|         | 4.3  |         | and Reading VRAM                             |      |

| 5.      | DESC | RIPTIO  | N OF THE VDP REGISTERS                       | 5-1  |

|         | 5.1  |         | rite-Only Registers                          |      |

|         |      | 5.1.1   | Register O (Contains Two VDP Control Bits)   |      |

|         |      | 5.1.2   | Register 1 (Contains Eight VDP Control Bits) | 5-1  |

|         |      | 5.1.3   | Register 2                                   | 5-2  |

|         |      | 5.1.4   | Register 3                                   | 5-3  |

|         |      | 5.1.5   | Register 4                                   | 5-3  |

|         |      | 5.1.6   | Register 5                                   | 5-4  |

|         |      | 5.1.7   | Register 6                                   | 5-4  |

|         |      | 5.1.8   | Register 7                                   |      |

|         | 5.2  |         | Inly Status Register                         |      |

|         |      | 5.2.1   | Interrupt Flag (F)                           |      |

|         |      | 5.2.2   | Coincidence Flag (C)                         |      |

|         |      | 5.2.3   | Fifth Sprite Flag (5S) and Number            | 5-6  |

| 6.      |      |         | THE VDP                                      |      |

|         | 6.1  |         | ng the Right Mode                            |      |

|         |      | 6.1.1   | Graphics I Mode Initialization               |      |

|         |      | 6.1.2   | Graphics II Mode Initialization              |      |

|         |      | 6.1.3   | Multicolor Mode Initialization               |      |

|         |      | 6.1.4   | Text Mode Initialization                     | 6-5  |

| 7.      |      |         | TTERNS                                       |      |

|         | 7.1  |         | erns Are Created Equal                       |      |

|         |      | 7.1.1   | Defining Patterns for Text                   |      |

|         |      | 7.1.2   | Defining Patterns for Sprites                | 7-4  |

| 8.  | THE DIFFE  | RENT DISPLAY MODES              |

|-----|------------|---------------------------------|

|     | 8.1 Grap   | hics I Mode                     |

|     | 8.1.       | The Pattern Table               |

|     | 8.1.       |                                 |

|     | 8.1.       |                                 |

|     | 8.2 Grap   | hics II Mode                    |

|     | -          | Pattern Table                   |

|     | 8.3.       |                                 |

|     | 8.4 The    | Name Table                      |

|     | 8.4.       |                                 |

|     | 8.4.       |                                 |

|     | 8.5 Text   | Mode                            |

|     | 8.5.       |                                 |

|     | 8.5.       |                                 |

|     | 8.6 Mult   | icolor Mode                     |

| 9.  | SPRITES .  |                                 |

|     |            | Sprite Pattern Table            |

|     |            | Sprite Attribute Table          |

|     | 9.2.       |                                 |

|     | 9.2.       |                                 |

|     | 9.2.       |                                 |

|     | 9.2.       |                                 |

|     | 0.2.       | opine color and carry clock bit |

| 10. | PROGRAM    | MING TIPS                       |

|     | 10.1 Horiz | contal and Vertical Scrolling   |

|     |            | nating Sprites                  |

|     |            | e Coincidence                   |

# **APPENDICES**

| APPENDIX     |                                                               | PAGE |

|--------------|---------------------------------------------------------------|------|

| Α.           | REGISTER VRAM LOOKUP TABLES                                   | Δ-1  |

| В.           | CPU TO VDP ACCESS TIMES.                                      |      |

| C.           | PATTERN GRAPHICS ADDRESS LOCATION TABLES                      |      |

| D.           | IC PINOUTS FOR TMS9918A/28A/29A AND TMS9118/28/29             |      |

| E.           | DEMO ASSEMBLY LANGUAGE PROGRAMS                               |      |

| F.           | SPECIAL CHARACTER SET FOR GRAPHICS MODES                      |      |

| G.           | GRAPHICS WORKSHEET                                            |      |

|              | LIST OF ILLUSTRATIONS                                         |      |

| 501155       |                                                               |      |

| FIGURE       |                                                               | PAGE |

| 1-1          | VDP Flow of Operation                                         | 1-1  |

| 2-1          | VDP Display Planes                                            |      |

| 3-1          | CPU to VDP Interface                                          | 3-1  |

| 6-1          | Register Initialization                                       |      |

| 6-2          | Graphic I Mode VRAM Memory Map                                |      |

| 6-3          | Graphic II Mode VRAM Memory Map                               |      |

| 6-4          | Multicolor Mode VRAM Memory Map                               |      |

| 6-5          | Text Mode VRAM Memory Map                                     |      |

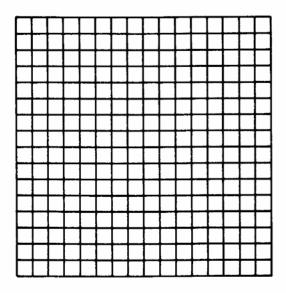

| 7-1          | 8x8 Pixel Pattern Grid                                        |      |

| 7-2          | Example 8x8 Pixel Patterns                                    |      |

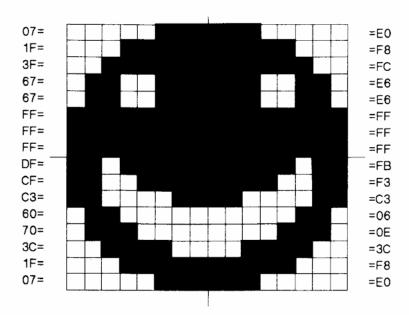

| 7-3          | Hexidecimal Conversion                                        |      |

| 7-4          | Pattern Table                                                 |      |

| 7-5          | 6x8 Pixel Pattern Grid for Text Mode                          |      |

| 7-6          | 8x8 Sprite Grid and Sprite Table                              |      |

| 7-7          | 16x16 Sprite Grid                                             |      |

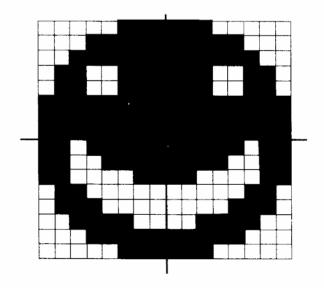

| 7-8          | Size 1 Sprite Pattern                                         |      |

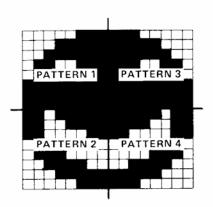

| 7-9          | Size 1 Sprite Organization                                    |      |

| 7-10         | Sprite Pattern Table                                          |      |

| 8-1          | Graphics I Mode Name Table Mapping                            |      |

| 8-2          | Graphics I Mode Mapping                                       |      |

| 8-3          | Pattern/Color Display Mapping                                 |      |

| 8-4          | Graphics II Mode Name Table Segmented Into Three Equal Blocks |      |

| 8-5          | Graphics II Mode Mapping                                      |      |

| 8-6          | Graphics II Pattern Table Arranged for Bit-Mapped Graphics    |      |

| 8-7          | Text Mode Name Table Pattern Positions                        |      |

| 8-8          | Pattern Graphics Name Table Mapping                           |      |

| 8-9          | 6x8 Pixel Pattern Grid for Text Mode                          |      |

| 8-10         | Mapping of VRAM Into the Pattern Plane in Text Mode           |      |

| 8-11<br>8-12 | Mapping an 8x8 Pixel Multicolor Pattern                       |      |

| 8-12<br>9-1  | Multicolor Mapping Scheme                                     |      |

| 9-1          | Sprite Attribute Table As Related to Sprite Planes            |      |

| 9-2<br>9-3   | Sprite Attribute Table Entry                                  |      |

| 9-3<br>9-4   | Vertical Sprite Positioning                                   |      |

| J-4          | Horizontal Sprite Positioning                                 | 3-4  |

| 10-3 |

|------|

|      |

|      |

| PAGE |

| 2-3  |

|      |

|      |

| 4-1  |

|      |

|      |

| 6-2  |

| 6-3  |

| 6-7  |

| 6-9  |

|      |

|      |

| 10-4 |

|      |

#### 1. INTRODUCTION

This is the first in a series of publications concerned with programming Texas Instruments Video Display Processors. This programmer's guide will pay close attention to the fundamentals of initializing and creating a display with the TMS9118/28/29 VDPs. The book also covers their predecessors, the TMS9918A/28A/29A VDPs, and serves as a prerequisite to future publications on the next generation of Texas Instruments Advanced Video Display Processors. Device differences are noted for your convenience.

The programming approach in this publication is at the assembly language level. Most programming examples are very general for the sake of clarity. Actual working programs written in 8088, 6502, TMS 7000, and TMS 9995 assembly languages are included in Appendix E.\*

All necessary subjects about programming a VDP are covered in this programmer's guide. If a subject is not at first discussed thoroughly enough or if more information about a particular subject is desired, let the Table of Contents guide you to a more detailed discussion of that topic.

#### 1.1 GENERAL VDP OPERATION

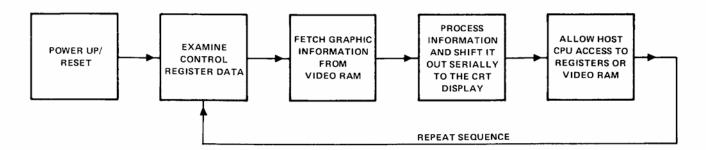

The VDP fetches data from Video RAM (VRAM) and processes it into a serial stream of data used to control the beam of a CRT as it sweeps across the screen. The VDP performs this operation over and over again, much like a program executing in a loop. The VDP does, however, perform many more functions in this simulated loop (see Figure 1-1).

FIGURE 1-1 — VDP FLOW OF OPERATION

Much of the VDP's versatility stems from the fact that it is not restricted to fetching data from the same place in memory in the same sequence. The VDP has nine internal registers, eight of which contain option and control bits which may be programmed by the user. The ninth register is the Status Register and may be read by the user in order to determine certain things that are happening within the VDP. By programming information into the eight control registers, the VDP can be directed to fetch data from different VRAM locations in various sequences.

The VDP takes time out every few microseconds to see if the host CPU would like access to one of its internal registers or VRAM. If the VDP did not perform this function, it would not be possible to program the internal registers, read the status, or even load an artistic masterpiece into VRAM for display.

<sup>\* 8088</sup> is a registered trademark of the Intel Corporation, and 6502 is a registered trademark of MOS Technology.

#### 1.2 REFERENCE MATERIAL

- 1) TMS9918A/28A/29A Video Display Processors Data Manual (MPO10A)

- 2) TMS9118/28/29 Video Display Processors Data Manual (SPPS002)

- 3) TMS9928/29 and TMS9128/29 Interface to Color Monitors Application Report (SPPA004)

- 4) TMS9118/TMS9128/TMS9129 Evaluation Module User's Guide (SPPU003)

- 5) Dual Video Display Processor Application Report (SPPA005)

# FEATURES

#### 2.1 DISPLAY PLANES

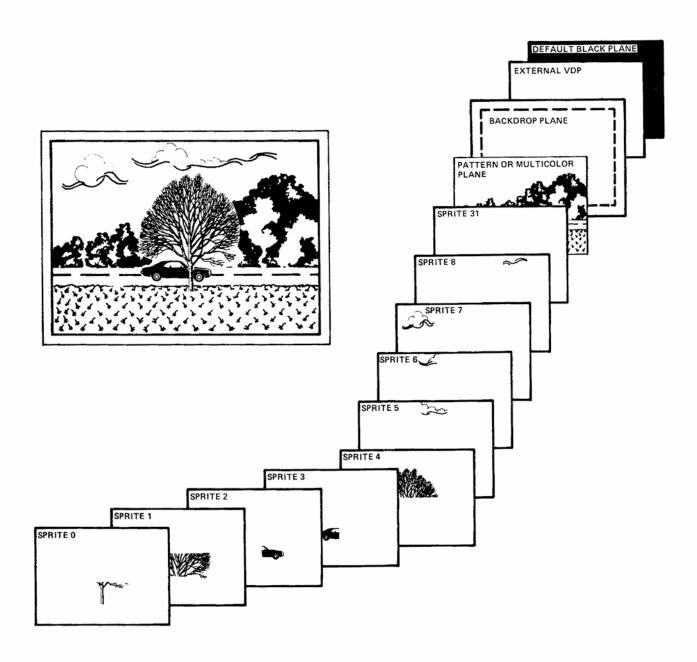

The VDP displays an image on the screen that can best be thought of as a set of 35 display planes stacked on top of one another (see Figure 2-1). Looking at a monitor or television screen, we can visualize the highest priority plane as the closest to us and the lowest priority plane as the plane farthest away.

If patterns on different planes happen to be occupying the same spot on the screen, then the pattern on the highest priority plane will show through at that spot. For a particular pattern on a plane to show through, any pattern on higher priority planes directly in front of it must be set to the VDP color 'transparent'. See the TMS9118/28/29 Video Display Processors Data Manual (SPPS002) for more details.

The 35 prioritized planes are shown in Figure 2-1, with each of the first 32 planes containing a single sprite. A sprite is a definable object whose position on the screen is relative to X,Y coordinates. The X,Y coordinates are composed of two bytes in VRAM. By changing the data in these two bytes, a sprite can be moved smoothly around the screen to an X,Y position of one pixel. Sprites are available in two sizes, either 8x8 pixels or 16x16 pixels. These sprites can also be magnified to 16x16 or 32x32 pixels.

Behind the 32 Sprite Planes is the Pattern Plane. This plane is used to display either graphics or text. The VDP can display patterns on this plane in one of four possible modes: Text, Graphics I, Graphics II, or Multicolor.

#### 2.2 DISPLAY MODES

Text Mode breaks the screen down into 6x8 pixel blocks specifically designed for displaying text. In Graphics I Mode, the screen is broken up into 32 horizontal blocks by 24 vertical blocks. Each block in Graphics I Mode contains 8x8 pixels, yielding a total screen resolution of 256x192 pixels. In Graphics II Mode, the screen breakdown and resolution are the same as in Graphics I Mode, but more complicated color and pattern displays are possible. Multicolor Mode is a low-resolution display mode which divides the screen into 64 horizontal blocks by 48 vertical blocks. Each block in Multicolor Mode contains 4x4 pixels and may be one of the sixteen colors available.

Behind the Pattern Plane is the Backdrop, which is larger in area than the other planes so that it forms a border around the other planes. The color of the Backdrop is defined by four bits in VDP Register 7.

The 35th and lowest priority plane is the External VDP Plane. If the output of a second VDP (slave) is detected by the main VDP (master), then all 35 planes generated by the second VDP will show through on this 35th plane. For an entity on the 35th plane to show through, all planes in front of the 35th plane must be transparent at that point.

FIGURE 2-1 - VDP DISPLAY PLANES

# 2.3 AVAILABLE COLORS

The VDP can display 16 colors (including transparent) as shown in Table 2-1. The VDP can also display fifteen different gray levels on monochrome monitors.

TABLE 2-1 — VDP COLOR ASSIGNMENTS

| COLOR NUMBER<br>(IN HEX) | ACTUAL COLOR     | COLOR NUMBER<br>(IN HEX) | ACTUAL COLOR     |  |  |

|--------------------------|------------------|--------------------------|------------------|--|--|

| 0                        | Transparent      | 8                        | Medium Red       |  |  |

| 1                        | Black            | 9                        | Light Red        |  |  |

| 2                        | Medium Green     | А                        | Dark Yellow      |  |  |

| 3                        | Light Green      | В                        | Light Yellow     |  |  |

| 4                        | Dark Blue        | С                        | Dark Green       |  |  |

| 5                        | Light Blue       | D                        | Magenta (Purple) |  |  |

| 6                        | Dark Red         | E                        | Gray             |  |  |

| 7                        | Cyan (Aqua Blue) | F                        | White            |  |  |

#### 3. COMMUNICATION BREAKDOWN

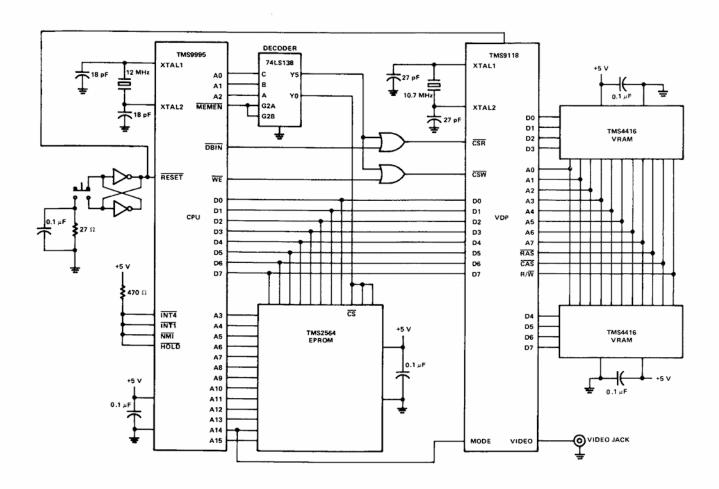

The circuit shown in Figure 3-1 is actually part of the Texas Instruments TMS9118/28/29 Evaluation Module (available for demonstration at your local TI Field Sales Office). We will use this circuit to help describe how the CPU and VDP communicate. This circuit is a complete working system.

FIGURE 3-1 — CPU TO VDP INTERFACE

#### 3.1 CPU TO VDP INTERFACE

The CPU communicates with the VDP through an eight-bit bidirectional data bus, three control lines, and an interrupt line. The three control signals are  $\overline{CSR}$  (chip select read),  $\overline{CSW}$  (chip select write), and MODE.  $\overline{CSR}$  and  $\overline{CSW}$  determine whether the VDP gets information off the data bus or puts information onto it. If  $\overline{CSR}$  is active, the VDP will output information for the CPU onto the data bus. If  $\overline{CSW}$  is active, the VDP will get information sent by the CPU off the data bus.

The MODE signal determines the VDP's source or destination for a data transfer. If the MODE signal is low, the VDP will do a VRAM operation. If the MODE signal is high, the VDP will do a VDP register operation.

One of the easiest ways to design the hardware interface is to set aside two addresses in the host CPU memory map for VDP communication. In the circuit shown in Figure 3-1, the two addresses set aside are Hex C000 and Hex C002. Performing a CPU operation at location Hex C000 will make the MODE signal low. Performing an operation at Hex C002 will make the MODE signal high.  $\overline{\text{CSR}}$  and  $\overline{\text{CSW}}$  are controlled by the CPU read/write logic. If a read operation is performed,  $\overline{\text{CSR}}$  will be active (low), and if a write operation is performed,  $\overline{\text{CSW}}$  will be active (low).

#### NOTE

The addresses you will use in a particular VDP system will probably be different than Hex C000 and Hex C002, but the function will be the same.

In order to have the full capability of each VDP graphics mode, our VDP must have 16K bytes of VRAM available. This is also the most popular amount of VRAM found in VDP systems. VRAM is located in the VDP memory map from Hex 0000 to Hex 3FFF. As described earlier, VRAM can only be accessed through the VDP by reading or writing from memory locations Hex C000 and Hex C002.

Another important note to make concerns the examples using address and data lines. Examples in this guide refer to the most significant data line bit (MSB) as D0 and the least significant data line bit (LSB) as D7. This also holds true for the 14 bit address bus, with A0 being the MSB and A13 being the LSB.

#### 3.2 SOFTWARE OPERATIONS

The CPU can be programmed to conduct one of four operations:

- Write a byte of data to VRAM

- 2) Read a byte of data from VRAM

- Write to one of the eight VDP internal registers, or set up the VRAM address by writing to the 14-bit Address Register

- Read the VDP Status Register.

Each of these operations requires one or more data transfers to take place from the CPU to the VDP. The VDP determines which of these four data transfers is being performed by the state of the three control signals (CSR, CSW, and MODE) as shown in Table 3-1.

TABLE 3-1 — CPU TO VDP DATA TRANSFERS

| OPERATION                | csw | CSR | MODE | PORT ADDRESS |

|--------------------------|-----|-----|------|--------------|

| Write to VRAM            | 0   | 1   | 0    | C000         |

| Read from VRAM           | 1   | 0   | 0    | C000         |

| Write to VDP register    | 0   | 1   | 1    | C002         |

| Read VDP Status Register | 1   | 0   | 1    | C002         |

# NOTE

Memory-mapped addresses >C000 and >C002 are arbitrary addresses chosen for this guide.

#### 4. TALKING TO THE VDP

#### 4.1 WRITING TO THE VDP REGISTERS

The VDP has eight write-only registers and one read-only Status Register. The write-only registers contain information that controls the operation of the VDP, including the way VRAM is allocated. The Status Register contains interrupt and sprite information.

A VDP write-only register is loaded using two eight-bit data transfers from the CPU. The first byte written is the data, and the second byte is the register number and tells the VDP where to put the data just sent to it. The MSB of the second byte must be a 1, the next four bits must be 0s, and the lowest three bits are the actual register number (from 0 to 7). Table 4-1 shows the format for the eight write-only registers.

| OPERATION                   | MSB<br>0 | 1  | 2  | 3  | 4  | 5  | 6  | LSB<br>7 | CSR | csw | MODE |

|-----------------------------|----------|----|----|----|----|----|----|----------|-----|-----|------|

| Data Write<br>(Byte 1)      | D0       | D1 | D2 | D3 | D4 | D5 | D6 | D7       | 1   | 0   | 1    |

| Register Select<br>(Byte 2) | 1        | 0  | 0  | 0  | 0  | Rn | Rn | Rn       | 1   | 0   | 1    |

**TABLE 4-1 — WRITE TO VDP REGISTERS**

#### EXAMPLE 4-1.

Let's say we wish to initialize Register 0 (R0) with a value of Hex 00. The first byte written to address Hex C002 will be Hex 00, the second byte will be Hex 80 (remember from Table 4-1 that the MSB must be set to 1). If we had wanted to write Hex 00 to Register 7 (R7), then the second byte transferred would have been Hex 87. If Hex 00 was to be written to Register 7 (R7), then the second byte transferred would be Hex 87.

#### 4.2 READING THE VDP STATUS REGISTER

The Status Register contents can be read with a single byte transfer, just by doing a read from address Hex C002 (see Table 4-2).

| OPERATION             | MSB<br>0 | 1  | 2  | 3  | 4  | 5  | 6  | LSB<br>7 | CSR | csw | MODE |

|-----------------------|----------|----|----|----|----|----|----|----------|-----|-----|------|

| Data Read<br>(Byte 1) | D0       | D1 | D2 | D3 | D4 | D5 | D6 | D7       | 0   | 1   | 1    |

TABLE 4-2 — READ FROM STATUS REGISTER

#### 4.3 WRITING AND READING VRAM

The VDP is connected to VRAM via a 14-bit autoincrementing Address Register. Once the address to read from or write to is set up (two-byte data transfer), we can read or write a byte of data using a one-byte transfer. Continuing to read or write to the VDP causes the address to increment automatically. Therefore, reading or writing a sequential chunk of data can be performed very quickly. The MODE signal is high (MODE1) for the first two data transfers (address setup), and low (MODE0) for the third when actually reading from or writing to VRAM.

The following sequences illustrate the proper steps for writing to and reading from VRAM. Refer to Table 4-3 and Table 4-4 for details.

#### Write to VRAM

- Transfer lower eight bits of address to MODE HIGH.

- 2) Transfer upper eight bits of address to MODE HIGH. (The two MSBs must be set to 0 and 1, respectively.)

- 3) Write a byte to MODE LOW.

- 4) Write next byte.

TABLE 4-3 -- WRITE TO VRAM

| OPERATION                                           | MSB<br>0 | 1       | 2        | 3        | 4        | 5        | 6        | LSB<br>7 | CSR | csw | MODE |

|-----------------------------------------------------|----------|---------|----------|----------|----------|----------|----------|----------|-----|-----|------|

| Setup Address<br>(Byte 1)                           | A6       | Α7      | A8       | А9       | A10      | A11      | A12      | A13      | 1   | 0   | 1    |

| Setup Address<br>(Byte 2)<br>Write Data<br>(Byte 3) | 0<br>D0  | 1<br>D1 | A0<br>D2 | A1<br>D3 | A2<br>D4 | A3<br>D5 | A4<br>D6 | A5<br>D7 | 1   | 0   | 0    |

#### Read from VRAM

- 1) Transfer lower eight bits of address to MODE HIGH.

- 2) Transfer upper eight bits of address to MODE HIGH. (The two MSBs must be set to 0.)

- 3) Read a byte from MODE LOW.

- 4) Read next byte.

TABLE 4-4 --- READ FROM VRAM

| OPERATION                              | MSB<br>0 | 1       | 2        | 3   | 4        | 5        | 6        | LSB<br>7 | CSR | csw | MODE |

|----------------------------------------|----------|---------|----------|-----|----------|----------|----------|----------|-----|-----|------|

| Setup Address<br>(Byte 1)              | A6       | Α7      | A8       | A9  | A10      | A11      | A12      | A13      | 1   | 0   | 1    |

| Setup Address<br>(Byte 2)<br>Read Data | 0<br>D0  | 0<br>D1 | A0<br>D2 | A1  | A2<br>D4 | A3<br>D5 | A4<br>D6 | A5<br>D7 | 1   | 0   | 1    |

| (Byte 3)                               |          |         |          | - 0 |          | - 0      |          |          |     | ·   |      |

#### EXAMPLE 4-2.

#### Write To VRAM

Suppose we wish to write Hex 00 to VRAM location Hex 20A0. The first byte transferred to address Hex C002 would be the lower address byte or Hex A0. The second byte transferred to address Hex C002 is the upper eight address bits with the two MSBs set to 0 and 1, respectively. Therefore, Hex 60 would be sent as the second byte instead of Hex 20. Now that the address is set up, a byte of data can be written to Hex 20A0 by a doing a write to address Hex C000.

#### EXAMPLE 4-3.

# Read From VRAM

Suppose we wish to read the byte of VRAM located at Hex 20A0. The first byte transferred to address Hex C002 would be the lower address byte or Hex A0. The second byte transferred to address Hex C002 is the upper eight address bits or Hex 20. The address is now set up, and location Hex 20A0 can be read by doing a read from address Hex C000.

#### 5. DESCRIPTION OF THE VDP REGISTERS

#### 5.1 VDP WRITE-ONLY REGISTERS

The eight VDP registers are described in the following paragraphs. Registers 0 and 1 contain bits to enable or disable various features and modes. Registers 2 through 6 contain values that specify the starting locations of various tables in VRAM. These VRAM tables are used to generate displays on the Pattern Plane and Sprite Planes. Register 7 contains the color of text (if in Text Mode) and contains the Backdrop color for all modes.

In some of the registers not all eight bits are used. To insure software compatibility with the next generation Advanced Video Display Processor, the unused bits must be set to 0s.

#### NOTE

Bit 0 is the MSB, and Bit 7 is the LSB.

#### 5.1.1 Register 0 (Contains Two VDP Control Bits)

Bit 6 = M3 (Pattern Mode Bit 3)

This is one of three bits that, when set, determine the display mode the VDP is in. The other two mode bits are located in Register 1.

| <u>M1</u> | <u>M2</u> | <u>M3</u> | Display Mode     |

|-----------|-----------|-----------|------------------|

| 0         | 0         | 0         | Graphics   Mode  |

| 0         | 0         | 1         | Graphics II Mode |

| 0         | 1         | 0         | Multicolor Mode  |

| 1         | 0         | 0         | Text Mode        |

Bit 7 = External VDP Plane Enable/Disable

**0-Disables External VDP Plane**

1-Enables External VDP Plane

#### 5.1.2 Register 1 (Contains Eight VDP Control Bits)

**REGISTER 1**

MSB LSB D7 D<sub>0</sub> 4/16 BLK. SPR. SPR. 0 ΙE M1 М2 SIZE MAG. ĸ SCRN

Bit 0 = 4/16K Selection

0-Selects 4K bytes of VRAM

1-Selects 16K bytes of VRAM.

#### NOTE

This bit is used only on the TMS9918A/28A/29A. When using TMS9118/28/29 this bit is a "Don't Care" and can be set to either state. The TMS9118/28/29 Family assumes 16K of VRAM is present.

Bit 1 = Display Blank Enable/Disable

0-Causes the active display area to blank

1-Enables the active display

Blanking causes the Sprite and Pattern Planes to blank but still allows the Backdrop color to show through. Blanking the display does not destroy any tables in VRAM.

Bit 2 = IE (Interrupt Enable)

0-Disables VDP interrupt

1-Enables VDP interrupt

If the VDP interrupt is connected in hardware and enabled by this bit, it will occur at the end of the active screen display area, just before vertical retrace starts. Exceptionally smooth, clean pattern drawing and sprite movement can be achieved by writing to the VDP during the period this interrupt is active.

Bit 3,4 = M1,M2 (Pattern Mode Bits 1 and 2)

Refer to Bit 6 of Register 0 for a description of these bits.

Bit 5 = Reserved Bit (must be set to 0)

Bit 6 = Sprite Size Select

O-Selects Size O sprites (8x8 pixels)

1-Selects Size 1 sprites (16x16 pixels)

Bit 7 = Sprite Magnify Option

0-Selects no magnification

1-Selects a magnification of 1, thus 8x8 sprites become 16x16 and 16x16 sprites become 32x32.

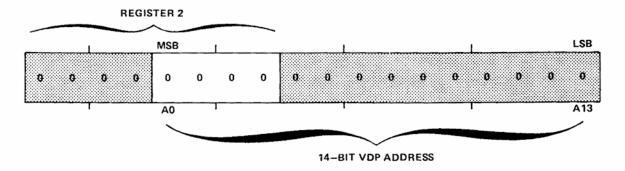

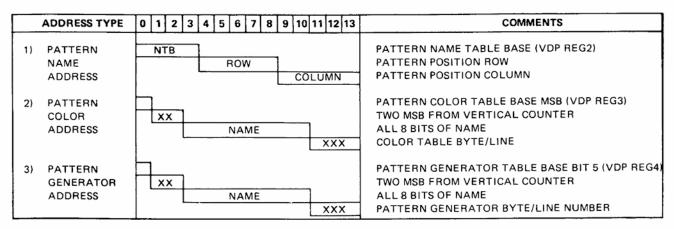

### 5.1.3 Register 2

Register 2 tells the VDP where the starting address of the Name Table is located in VRAM. The range of its contents is from 0-F. The contents of the register form the upper four bits of the 14-bit VDP address, therefore making the location of the Name Table in VRAM equal to (Register 2) \* 400 (Hex).

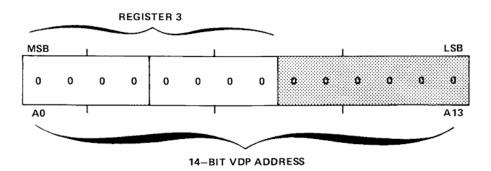

#### 5.1.4 Register 3

Register 3 tells the VDP where the starting address of the Color Table is located in VRAM. The range of its contents is from 0-FF. The contents of the register form the upper eight bits of the 14-bit VDP address, therefore making the location of the Color Table in VRAM equal to (Register 3) \* 40 (Hex).

#### NOTE

Register 3 functions differently when the VDP is in Graphics II Mode. In this mode the Color Table can only be located in one of two places in VRAM, either Hex 0000 or Hex 2000. If Hex 0000 is where you wish the Color Table to be located, then the MSB in Register 3 has to be a 0. If Hex 2000 is the location choice for your Color Table, then the MSB in Register 3 must be a 1. In either case, all the LSBs in Register 3 must be set to 1s. Therefore, in Graphics II Mode the only two values that work correctly in Register 3 are Hex 7F and Hex FF.

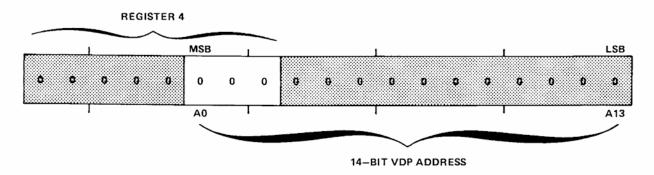

#### 5.1.5 Register 4

Register 4 tells the VDP where the starting address of the Pattern Table is located in VRAM. The range of its contents is from 0-7. The contents of the register form the upper three bits of the 14 bit VDP address, therefore making the location of the Pattern Table in VRAM equal to (Register 4) \* 800 (Hex).

Register 4 functions differently when the VDP is in Graphics II Mode. In this mode the Pattern Table can only be located in one of two places in VRAM, either Hex 0000 or Hex 2000. If Hex 0000 is where you wish the Pattern Table to be located, then the MSB in Register 4 has to be a 0. If Hex 2000 is the location choice for your Pattern Generator Table, then the MSB in Register 4 must be a 1. In either case, all the LSBs in Register 4 must be set to 1s. Therefore, in Graphics II Mode the only two values that work correctly in Register 4 are Hex 03 and Hex 07.

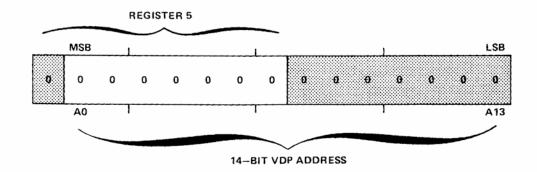

#### 5.1.6 Register 5

Register 5 tells the VDP where the starting address of the Sprite Attribute Table is located in VRAM. The range of its contents is from 0-7F. The contents of the register form the upper seven bits of the 14 bit VDP address, therefore making the location of the Sprite Attribute Table in VRAM equal to (Register 5) \* 80 (Hex).

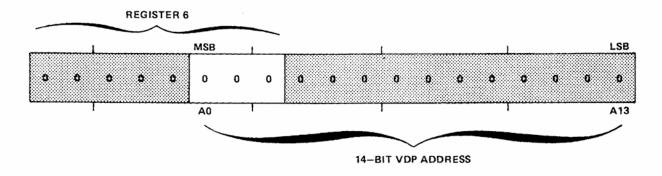

#### 5.1.7 Register 6

Register 6 tells the VDP where the starting address of the Sprite Pattern Table is located in VRAM. The range of its contents is from 0-7. The contents of the register form the upper three bits of the 14 bit VDP address, therefore making the location of the Sprite Pattern Table in VRAM equal to (Register 6) \* 800 (Hex).

#### 5.1.8 Register 7

The upper four bits of Register 7 contain the color of bits on in Text Mode. The lower four bits contain the color of bits off in Text Mode and the Backdrop color in all modes.

#### 5.2 READ-ONLY STATUS REGISTER

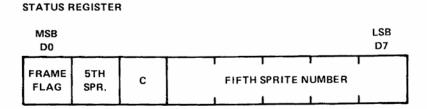

The VDP Status Register contains the Interrupt Flag, Coincidence Flag, Fifth Sprite Flag, and the Fifth Sprite Number (if one exists). Each of these is explained in the following paragraphs.

#### 5.2.1 Interrupt Flag (F)

The F flag in the Status Register is set equal to 1 at the end of the raster scan of the last line of the active display, just before the Backdrop color at the bottom of the screen begins. It is reset to a 0 after the Status Register is read or whenever the VDP is externally reset (hardware reset). If the Interrupt Enable bit located in VDP Register 1 is active (1), then the VDP interrupt output line (INT) will be active (0) whenever the F status flag is 1.

#### NOTE

The Status Register needs to be read frame-by-frame in order to clear the interrupt and receive the new interrupt for the next frame.

#### 5.2.2 Coincidence Flag (C)

The C status flag will be set to a 1 if two or more sprites coincide. Coincidence occurs if any two sprites on the screen have at least one overlapping pixel. Sprites set to the VDP color transparent, as well as those partially or completely off the screen, are considered. Sprites beyond the Attribute Table terminator of Hex D0 are not considered. The C flag is cleared whenever the VDP Status Register is read or the VDP is externally reset.

# 5.2.3 Fifth Sprite Flag (5S) and Number

The Fifth Sprite Flag is set to a 1 whenever there are five or more sprites active on a horizontal line. The Fifth Sprite Flag is cleared to a 0 after the Status Register is read or whenever the VDP is externally reset. The number of the lowest priority sprite on the horizontal line is loaded into the lower five bits of the Status Register whenever the Fifth Sprite Flag is set and is valid whenever the Fifth Sprite Flag is a 1. The setting of the Fifth Sprite Flag will not generate an interrupt.

#### 6. INITIALIZING THE VDP

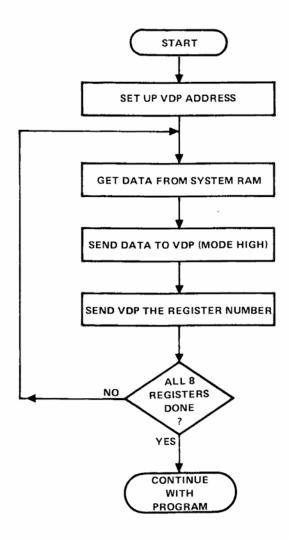

After powerup of our VDP system, the first thing to be done is register initialization. In order to do this we need to know a few things, such as which pattern display mode to use and where in VRAM we are going to place the tables required. Figure 6-1 shows a procedure for initializing all eight VDP registers. The next section is a brief description of the popular uses for each mode.

FIGURE 6-1 - REGISTER INITIALIZATION

#### 6.1 CHOOSING THE RIGHT MODE

Most applications displaying text use either Text or Graphics I Mode. Video games needing a high-resolution display normally use Graphics I or Graphics II Mode. Graphics I Mode is a bit more popular for games because a colorful, detailed, high-resolution picture can be generated using very little data. Graphics II Mode is used when a high-resolution picture needs extremely fine detail and color or when you wish to organize memory in a bit-map arrangement for calculating pixels, lines, circles, etc. The Graphics II Mode bit-map arrangement is also very popular for personal computer business graphics. Multicolor Mode is popular for games requiring only a low-resolution display. Sprites are available in all modes except Text and are primarily used for objects that move and change shape (animation).

Detailed descriptions of Graphics I, Graphics II, Text, and Multicolor Mode appear in Section 8. Refer to these sections to decide which display mode is best suited to your particular application.

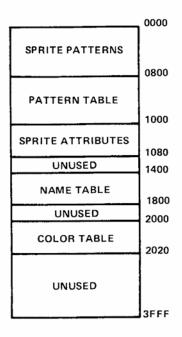

Some typical table values used to initialize the registers in each graphic mode are shown and described in the following figures. The resulting VRAM Memory Map is shown after the table values. Actual assembly language programs written for various CPUs and using the following register initialization values are included in Appendix E.

The typical register initialization values are given here only as one example. Those of you preferring a different VRAM memory map can either calculate the values as described in Section 5 or refer to the Register Address Look-Up Tables provided in Appendix A.

#### 6.1.1 Graphics I Mode Initialization

TABLE 6-1 — GRAPHIC I MODE INITIALIZATION

| REGISTER | MSB LSB  | HEX | DESCRIPTION                                          |  |

|----------|----------|-----|------------------------------------------------------|--|

| REG 0    | 00000000 | 00  | Graphics I Mode, No External Video                   |  |

| REG 1    | 11000000 | CO  | 16K,Enable Display,Disable Int.,8x8 Sprites,Mag.Off  |  |

| REG 2    | 00000101 | 05  | Address of Name Table in VRAM = Hex 1400             |  |

| REG 3    | 10000000 | 80  | Address of Color Table in VRAM = Hex 2000            |  |

| REG 4    | 0000001  | 01  | Address of Pattern Table in VRAM = Hex 0800          |  |

| REG 5    | 00100000 | 20  | Address of Sprite Attribute Table in VRAM = Hex 1000 |  |

| REG 6    | 00000000 | 00  | Address of Sprite Pattern Table in VRAM = Hex 0000   |  |

| REG 7    | 0000001  | 01  | Backdrop Color = Black                               |  |

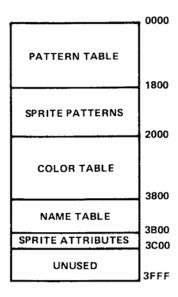

FIGURE 6-2 — GRAPHIC I MODE VRAM MEMORY MAP

# 6.1.2 Graphics II Mode Initialization

TABLE 6-2 — GRAPHIC II MODE INITIALIZATION

| REGISTER | MSB LSB  | HEX | DESCRIPTION                                              |

|----------|----------|-----|----------------------------------------------------------|

| REG O    | 00000010 | 02  | Graphics II Mode, No External Video                      |

| REG 1    | 11000010 | C2  | 16K, Enable Disp., Disable Int., 16x16 Sprites, Mag. Off |

| REG 2    | 00001110 | OE  | Address of Name Table in VRAM = Hex 3800                 |

| REG 3    | 11111111 | FF  | Address of Color Table in VRAM = Hex 2000                |

| REG 4    | 00000011 | 03  | Address of Pattern Table in VRAM = Hex 0000              |

| REG 5    | 01110110 | 76  | Address of Sprite Attribute Table in VRAM = Hex 3B00     |

| REG 6    | 00000011 | 03  | Address of Sprite Pattern Table in VRAM = Hex 1800       |

| REG 7    | 00001111 | OF  | Backdrop Color = White                                   |

FIGURE 6-3 — GRAPHIC II MODE VRAM MEMORY MAP

# 6.1.3 Multicolor Mode Initialization

TABLE 6-3 — MULTICOLOR MODE INITIALIZATION

| REGISTER | MSB LSB  | HEX | DESCRIPTION                                          |

|----------|----------|-----|------------------------------------------------------|

| REG O    | 00000000 | 00  | Multicolor Mode, No External Video                   |

| REG 1    | 11001011 | СВ  | 16K,Enable Display,Disable Int.,16x16 Sprites,Mag.On |

| REG 2    | 00000101 | 05  | Address of Name Table in VRAM = Hex 1400             |

| REG 3    | xxxxxxx  | xx  | Color Table not used. All bits are don't cares.      |

| REG 4    | 0000001  | 01  | Address of Pattern Table in VRAM = Hex 0800          |

| REG 5    | 00100000 | 20  | Address of Sprite Attribute Table in VRAM = Hex 1000 |

| REG 6    | 00000000 | 00  | Address of Sprite Pattern Table in VRAM = Hex 0000   |

| REG 7    | 0000001  | 04  | Backdrop Color = Dark Blue                           |

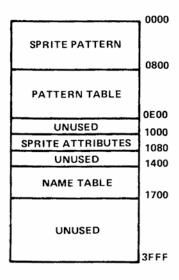

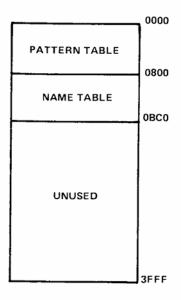

FIGURE 6-4 — MULTICOLOR MODE VRAM MEMORY MAP

# 6.1.4 Text Mode Initialization

**TABLE 6-4 — TEXT MODE INITIALIZATION**

| REGISTER | MSB LSB  | HEX | DESCRIPTION                                      |

|----------|----------|-----|--------------------------------------------------|

| REG 0    | 00000000 | 00  | Text Mode, No External Video                     |

| REG 1    | 11010000 | DO  | 16K,Enable Disp.,Disable Int.                    |

| REG 2    | 0000010  | 02  | Address of Name Table in VRAM = Hex 0800         |

| REG 3    | xxxxxxx  | xx  | Color Table not used. Color is defined in Reg. 7 |

| REG 4    | 00000000 | 00  | Address of Pattern Table in VRAM = Hex 0000      |

| REG 5    | xxxxxxx  | 20  |                                                  |

| REG 6    | xxxxxxx  | 00  |                                                  |

| REG 7    | 11110101 | F5  | White Text on Light Blue Background              |

FIGURE 6-5 — TEXT MODE VRAM MEMORY MAP

#### 7. CREATING PATTERNS

#### 7.1 ALL PATTERNS ARE CREATED EQUAL

If you can create 8x8 pixel patterns you can create fonts for Graphics I Mode, Graphics II Mode, Text Mode, and sprites. In the following pages we will define some patterns and show how they should be entered into VRAM in order to produce a display.

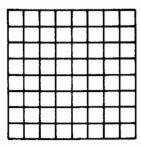

1) Figure 7-1 is a sample grid which will be used to create 8x8 pixel patterns. Each small square within the grid represents one pixel on the screen.

FIGURE 7-1 — 8X8 PIXEL PATTERN GRID

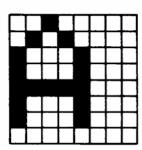

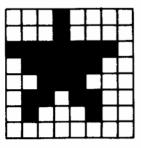

2) Fill in the squares within the grid to create your text, graphic, or sprite pattern. Examples of the letter "A", an arrow, and a star are shown in Figure 7-2.

FIGURE 7-2 — EXAMPLE 8X8 PIXEL PATTERNS

#### NOTE

If you are defining patterns to be used in Text Mode (40 patterns per line), the patterns should be left justified within a 6x8 pixel block like the letter "A" shown in Figure 7-2. Refer to Section 8.5 for a further description.

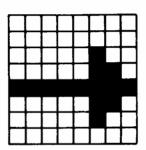

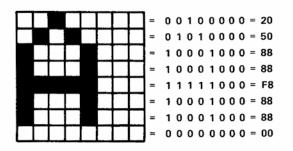

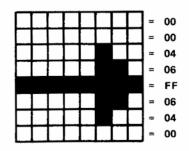

3) Now comes the task of converting the pattern to numbers. First assign 1s to the filled in squares and 0s to the blanks. Then convert the 1s and 0s to their hexadecimal equivalents as shown in Figure 7-3.

FIGURE 7-3 — HEXIDECIMAL CONVERSION

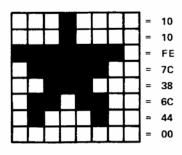

4) Now place the 8 bytes that define the pattern into the Pattern Table. Assume that the location of the Pattern Table in VRAM is defined to be Hex 800, and the arrow is to be named pattern number 00. Next place the eight bytes into the table as shown in Figure 7-4.

FIGURE 7-4 — PATTERN TABLE

#### 7.1.1 Defining Patterns for Text

When using text in your application, it is often convenient to place the eight bytes defining your text character in its actual ASCII number location. This will simplify writing text to the screen. Writing the ASCII value directly to the Name Table causes the appropriate character to appear on the screen. As shown in Example 7-1, a space character is contained in Pattern Table position Hex 20, and the letter "A" is contained in Pattern Table position Hex 41.

#### EXAMPLE 7-1.

```

ASCII Space = Hex 20

? = Hex 3F

A = Hex 41

B = Hex 42

C = Hex 43

Etc.

```

#### NOTE

When defining patterns for Text Mode, the pattern must be defined within a 6x8 pixel grid as shown in Figure 7-5. The two LSBs are unused and therefore not displayed by the VDP.

FIGURE 7-5 — 6X8 PIXEL PATTERN GRID FOR TEXT MODE

# 7.1.2 Defining Patterns for Sprites

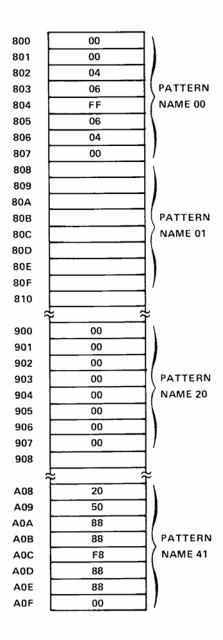

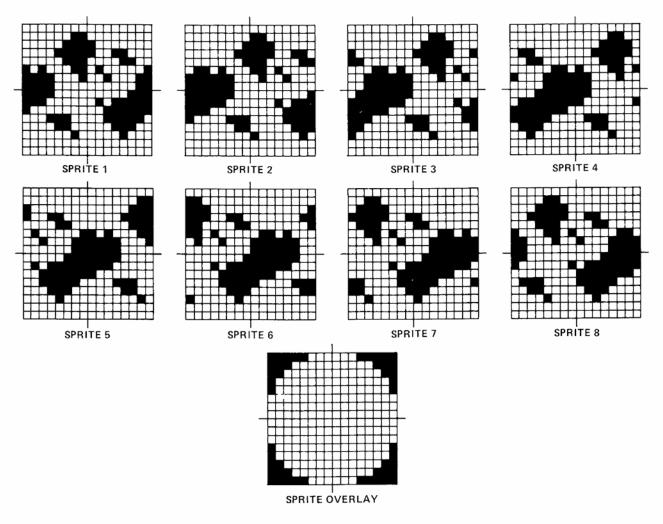

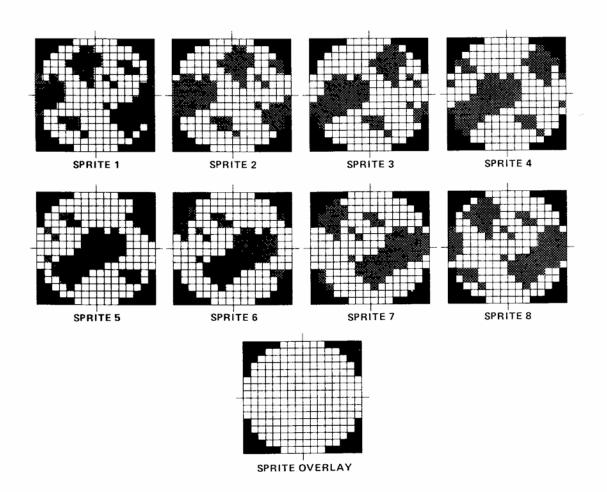

1) To use Size O sprites (8x8 pixels), the patterns are defined exactly like the arrow and the star shape done earlier with one change. Instead of entering the code in the Pattern Table, it is now entered into the Sprite Pattern Table. Figure 7-6 shows a sprite grid and the Sprite Generator Table for an 8x8 pixel sprite pattern.

FIGURE 7-6 — 8X8 SPRITE GRID AND SPRITE TABLE

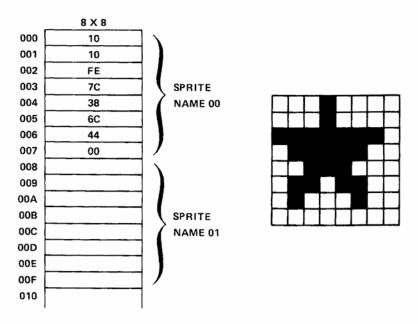

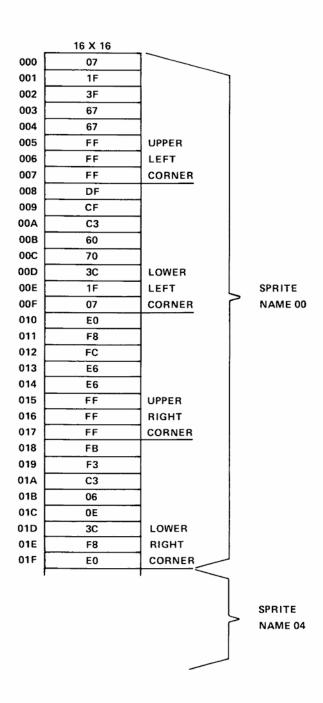

2) If you are going to use Size 1 sprites (16x16 pixels), then the patterns are still defined as 8x8 pixel patterns. It takes four 8x8 pixel patterns to form a 16x16 pixel grid as shown in Figure 7-7.

FIGURE 7-7 — 16X16 SPRITE GRID

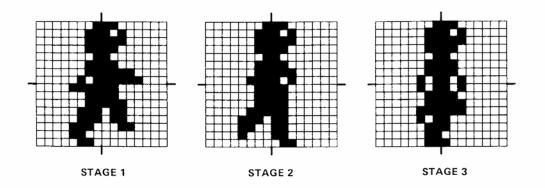

3) Fill in the squares to create your Size 1 sprite pattern. An example is shown in Figure 7-8.

FIGURE 7-8 — SIZE 1 SPRITE PATTERN

4) Next encode the sprite pattern. This is done by splitting the sprite into four sections as shown in Figure 7-9. The four 8x8 pixel patterns should be encoded in the following order.

Pattern 1 = upper left

Pattern 2 = lower left

Pattern 3 = Upper right

Pattern 4 = Lower right

FIGURE 7-9 — SIZE 1 SPRITE ORGANIZATION

5) Place the 32 bytes of information in the Sprite Pattern Table, assuming that the table in VRAM is located at Hex 0000. Figure 7-10 shows how the Sprite Generator Table looks for our 16x16 pixel sprite.

FIGURE 7-10 — SPRITE PATTERN TABLE

# 8. THE DIFFERENT DISPLAY MODES

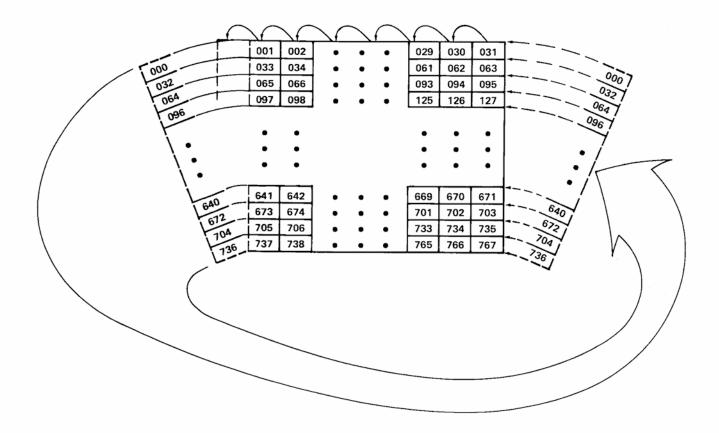

## 8.1 GRAPHICS I MODE

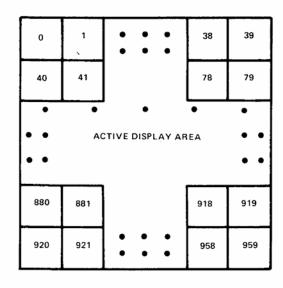

The VDP is in Graphics I Mode when all three mode bits (M1,M2,M3) located in VDP Registers 0 and 1 are set to zero. When in this mode, the Pattern Plane has a resolution of 256 horizontal pixels by 192 vertical pixels. The screen is broken up into blocks each containing an 8x8 pixel pattern. There are 32 of these blocks horizontally and 24 of them vertically. Figure 8-1 shows the position of these 768 blocks on the screen.

| ROW 0 000 001 002 003 • • 028 029 03               |         |                        |

|----------------------------------------------------|---------|------------------------|

| NOW 0 000   001   002   003   • •   028   029   03 | 0   031 | (HEX 01F)              |

| ROW 1 032 033 034 035 • • • 060 061 06             | 2 063   | (HEX 03F)              |

| ROW 2 064 065 066 067 • • • 092 093 09             | 4 095   | (HEX 05F)              |

| ROW 3 096 097 098 099 • • 124 125 12               | 6 127   | (HEX 07F)              |

|                                                    |         |                        |

| •   • •                                            |         | 1                      |

| ACTIVE DISPLAY AREA                                | •       |                        |

| ACTIVE DISPLAY AREA                                | •       |                        |

|                                                    | 0 671   | (HEX <b>29</b> F)      |

| • • •                                              |         | (HEX 29F)<br>(HEX 2BF) |

| ROW 20 640 641 642 643 • • 668 669 67              | 2 703   |                        |

FIGURE 8-1 — GRAPHICS I MODE NAME TABLE MAPPING

Three tables are required in VRAM in order to create a Graphics I Mode picture, these are the Name Table, Pattern Table, and the Color Table. If every possible bit of color and pattern detail is defined, a Graphics I Mode picture would take up 2848 (Hex B20) bytes.

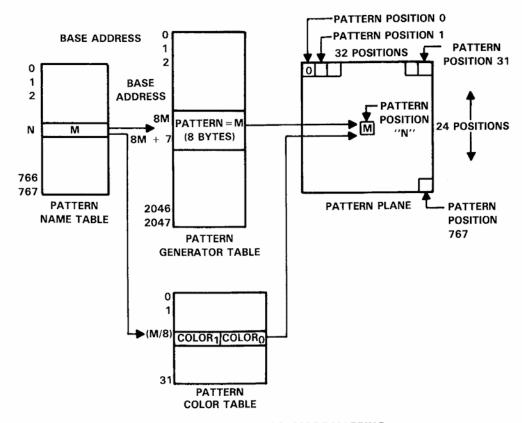

## 8.1.1 The Pattern Table

The Pattern Table contains a library of user defined patterns that can be displayed in any of the 768 screen positions. It is 2048 bytes long and is arranged as 256 eight byte patterns. Each one of these eight byte patterns defines an 8x8 pixel area. All of the 1s within a pattern designate one color (let's call this color 1), while all of the 0s designate another color (color 0).

A unique feature of Graphics I Mode, as opposed to bit-mapped graphics, is the fact that once an 8x8 pixel pattern has been defined and stored in the Pattern Table, it can be used multiple times on the screen without being redefined.

#### EXAMPLE 8-1.

If only the first eight byte pattern in the Pattern Table was defined (Pattern 0), you could place this pattern in every single one of the 768 screen positions by writing Hex 00 to every byte of the 768 byte Name Table.

# 8.1.2 The Name Table

As illustrated in Figure 8-1, there are 768 screen locations. Each of these locations is represented by one byte of memory located in the Name Table. The first byte of the Name Table specifies which pattern will be located in the upper left hand corner of the screen. The last

byte in the Name Table specifies the pattern for the lower right hand screen corner. Each byte entry in the Name Table can designate one of 256 (Hex FF) patterns. The location of the 768 byte Name Table in VRAM is defined by the base address located in VDP Register 2.

### 8.1.3 The Color Table

The Color Table for a Graphics I Mode picture is 32 bytes long. Its location in VRAM is determined by the eight-bit Color Table base address in VDP Register 3.

The color of the 1s and 0s within a pattern is defined by the Color Table. Each byte entry in the Color Table defines two colors. The upper nibble (four bits) defines the color of the 1s, and the lower nibble defines the color of the 0s. Since we can create 256 unique 8x8 pixel patterns but can only have 32 Color Table entries, each entry in the Color Table must define the color for more than one pattern. In fact, the first byte in the Color Table defines the color for the first eight patterns. Likewise, the second byte in the Color Table defines the color for the next eight patterns defined.

Table 8-1 illustrates the Graphics I Mode Color Table.

Figure 8-2 illustrates how the Pattern Table, Name Table, and Color Table are mapped to the screen.

TABLE 8-1 — GRAPHICS I MODE COLOR TABLE

| BYTE NO. | PATTERN NO. | BYTE NO. | PATTERN NO. |

|----------|-------------|----------|-------------|

| 0        | 07          | 16       | 128135      |

| 1        | 815         | 17       | 136143      |

| 2        | 1623        | 18       | 144151      |

| 3        | 2431        | 19       | 152159      |

| 4        | 3239        | 20       | 160167      |

| 5        | 4047        | 21       | 168175      |

| 6        | 4855        | 22       | 176183      |

| 7        | 5663        | 23       | 184191      |

| 8        | 6471        | 24       | 192199      |

| 9        | 7279        | 25       | 200207      |

| 10       | 8087        | 26       | 208215      |

| 11       | 8895        | 27       | 216223      |

| 12       | 96103       | 28       | 224231      |

| 13       | 104111      | 29       | 232239      |

| 14       | 112119      | 30       | 240247      |

| 15       | 120127      | 31       | 248255      |

FIGURE 8-2 — GRAPHICS I MODE MAPPING

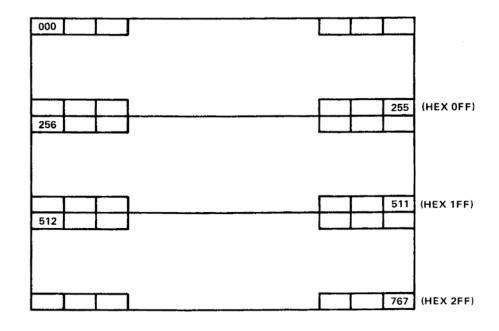

### 8.2 GRAPHICS II MODE

Graphics II Mode is similar to Graphics I Mode in the way the screen is organized. The resolution is still 256 horizontal pixels by 192 vertical pixels. Three tables are still required in VRAM in order to generate a display, these being the Name Table, Color Table, and Pattern Table. The Name Table is still 768 bytes long, but the length of the Color and Pattern Tables has been extended. Instead of having to choose from a library of 256 8x8 pixel patterns for display in the 768 screen locations (which means patterns have to be reused) you can define 768 8x8 pixel patterns in Graphics II Mode. This allows a unique pattern to be created for every possible screen location. Instead of one byte of color information for every eight patterns, there are now eight bytes of color information per pattern, thereby making the Pattern Table and the Color Table in Graphics II Mode the same length.

Since there are eight bytes of color information per pattern, two unique colors can be specified for each line of an 8x8 pixel pattern. This allows up to 16 colors within a pattern.

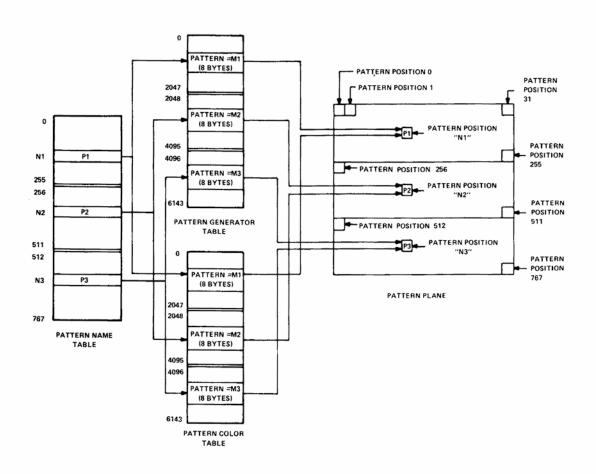

### 8.3 THE PATTERN TABLE

The Pattern Table is 6144 (Hex 1800) bytes long, assuming all patterns are defined, and is best thought of as three equal blocks of 2048 bytes of pattern information. Each of the three 2048 byte blocks is divided into 256 8x8 pixel pattern definitions. The first 256 patterns can only be displayed on the upper third of the screen. The second 256 patterns can only be displayed on the middle section of the screen, and the last 256 patterns can only be displayed on the lower third of the screen.

### 8.3.1 The Color Table

The Color Table is 6144 (Hex 1800) bytes long, assuming all colors are defined, and is segmented into three 2048 byte blocks exactly like the Pattern Table. Each 2048 byte block is divided into 256 color definitions, each being eight bytes long. The first 256 color definitions correspond directly to the first 256 patterns defined. Likewise, the second 256 color definitions correspond to the second 256 patterns, and the third 256 color definitions correspond to the last 256 patterns defined.

It takes eight bytes to define a pattern shape and eight bytes to define what color that pattern will be. Each byte in a color definition defines the color of the bits that are on or off for the corresponding line of the pattern. The upper four bits define the color of the bits on, the lower four bits define the color of the bits off in a line of the pattern. An example of how color is mapped to a pattern is shown in Figure 8-3.

|       |                   |       |       |      |      |              |          |   |   |         |   |   |   |   |               |   |   | 0 |             | 3  | 4   | 7            |       |

|-------|-------------------|-------|-------|------|------|--------------|----------|---|---|---------|---|---|---|---|---------------|---|---|---|-------------|----|-----|--------------|-------|

| ROW 0 | 0                 | 1     | 0     | 0    | 0    | 0            | 0        | 1 | E | 3       | 1 | В | В | В | В             | В | 1 | 1 | (BLACK)     |    | В   | (LT. YELLOW) | 0 ROW |

| 1     | 0                 | 0     | 1     | 0    | 0    | 0            | 1        | 0 |   | 3       | В | 7 | В | В | В             | 7 | В | 7 | (CYAN)      |    | В   | (LT. YELLOW) | 1     |

| 2     | 0                 | 0     | 0     | 1    | 0    | 1            | 0        | 0 |   | 3       | В | В | С | В | С             | 8 | В | С | (GREEN)     |    | В   | (LT. YELLOW) | 2     |

| 3     | 0                 | 0     | 0     | 0    | 1    | 0            | 0        | 0 | E | 3       | В | В | В | Ε | В             | В | В | E | (GRAY)      |    | 8   | (LT. YELLOW) | 3     |

| 4     | 0                 | 0     | 0     | 0    | 1    | 0            | 0        | 0 |   | 3       | В | В | В | 8 | В             | В | В | 8 | (MED. REI   | D) | В   | (LT. YELLOW) | 4     |

| 5     | 0                 | 0     | 0     | 0    | 1    | 0            | 0        | 0 | E | 3       | В | В | В | 5 | В             | В | В | 5 | (LT. BLUE   | )  | В   | (LT. YELLOW) | 5     |

| 6     | 0                 | 0     | 0     | 0    | 1    | 0            | 0        | 0 | 6 | 3       | В | В | В | 6 | В             | В | В | 6 | (DK. RED)   |    | В   | (LT. YELLOW) | 6     |

| 7     | 0                 | 0     | 0     | 0    | 1    | 0            | 0        | 0 | E | 3       | В | В | В | D | В             | В | В | D | (MAGENT     | A) | В   | (LT. YELLOW) | 7     |

|       | D.                | \ TT1 | - DNI | CEN  | IED  | <b>A T</b> O | <b>D</b> |   | • |         |   |   |   |   |               |   |   |   |             |    | 201 | 201.00       |       |

|       | PATTERN GENERATOR |       |       |      |      |              | PATTERN  |   |   |         |   |   |   |   | PATTERN COLOR |   |   |   |             |    |     |              |       |

|       |                   | T     | ABL   | E EN | ITR' | Y            |          |   |   | PATTERN |   |   |   |   |               |   |   |   | TABLE ENTRY |    |     |              |       |

FIGURE 8-3 — PATTERN/COLOR DISPLAY MAPPING

## 8.4 THE NAME TABLE

As in Graphics I Mode, the Name Table of Graphics II Mode contains 768 entries which correspond to each of the 768 pattern positions on the display screen. Because each Name Table entry is only one byte long, it can only specify one of 256 patterns (Hex FF). In order to be able to specify a unique pattern for each of the 768 pattern positions, the screen is broken up into three sections as shown in Figure 8-4. Each of the screen sections is 256 bytes long, and since a byte can specify 256 different values, a unique pattern can be specified for each screen location. An example of Graphics II Mode mapping is shown in Figure 8-5.

FIGURE 8-4 — GRAPHICS II MODE NAME TABLE SEGMENTED INTO THREE EQUAL BLOCKS

FIGURE 8-5 — GRAPHICS II MODE MAPPING

# 8.4.1 Graphics II Mode As a Bit-Mapped Display

A neat feature of Graphics II Mode is that it can be arranged by the programmer to act as a bit-mapped display. This is extremely useful when your application allows the use of an algorithm to calculate the position of pixels on the screen instead of hand drawing them (coding each pixel at a time). Using Graphics II Mode as a bit-map lets you address every pixel on the screen individually for plotting points, drawing lines, circles, etc. The only drawback to this arrangement is that even though the Pattern Plane is completely bit-mapped, the color assignments are not. Since a unique color cannot be specified for each pixel on the screen, one of two things can be done; use more than two colors (but be careful where you plot them on the screen) or use only two colors (pixels on could be one color, pixels off another) and not worry about where you plot.

The way to arrange Graphics II Mode as a bit-map is to write a different value to each of the 768 Name Table entries. This means that the VDP will map a unique Pattern Table entry to each screen position. By writing to a byte within an eight byte Pattern Table entry, any pixel on the screen can be turned on or off.

The simplest way to illustrate this point is to write the same value to each of the Color Table entries. A color value of Hex 4F written to all Color Table locations makes for nice blue pixels on a white background (pixels on will be blue, and pixels off will be white).

As stated earlier, to specify a bit-map a unique pattern is defined for each entry in the Name Table. An organized way to do this is to write Hex 00 to the first Name Table entry, Hex 01 to the second, Hex 02 to the third, and so forth. After reaching Hex FF the process is repeated twice more so that a dump of the 768 byte Name Table would render the values 0 - FF, 0-FF, 0-FF.

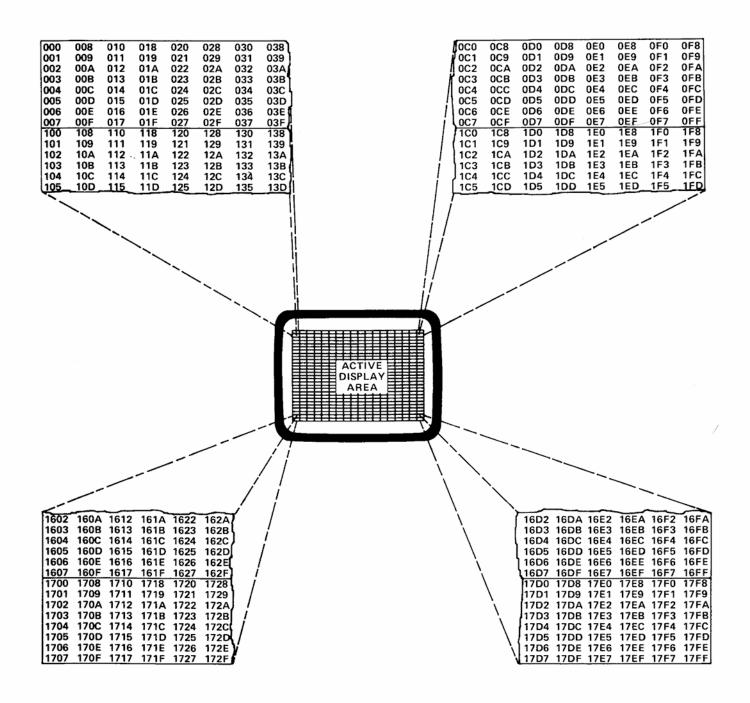

At this point we can forget about the Name Table and the Color Table and concentrate on the Pattern Table. Each bit within a Pattern Table byte entry now represents a unique pixel on the screen. Figure 8-6 illustrates how the Pattern table is currently mapped to the screen. This figure assumes that the location of the Pattern Table in VRAM starts at Hex 0000.

FIGURE 8-6 — GRAPHICS II PATTERN TABLE ARRANGED FOR BIT-MAPPED GRAPHICS

Looking at Figure 8-6 we can see that in order to turn on the pixel located in the upper lefthand corner of the display we would write Hex 80 to the first byte of the Pattern Table (location Hex 0000). Likewise, to turn on the pixel at the bottom righthand screen edge Hex 01 would be written to location Hex 1755.

At this point we can do ourselves a favor by writing a routine that, given any X,Y coordinates, will tell us the address of the byte we wish to write to and the data we need to write to it. The following is a step-by-step procedure of one way to calculate the address and the data.

#### EXAMPLE 8-2.

INPUTS: X = Hex 00-FF or Decimal 0-255Y = Hex 00-C0 or Decimal 0-192

- Take the integer value of (X/8) and multiply it times 8. This will give the horizontal byte offset. The actual bit we need to plot is determined by whatever remainder is left after calculating (X/8).

- 2) Take the integer value of (Y/8) and multiply it times Hex 100. This will give the vertical byte offset to the nearest eight bits. If there is any remainder after calculating (Y/8), add it to the vertical byte offset. This gives the vertical starting address.

- 3) Add the horizontal byte offset to the vertical starting address. This will give the actual address of the byte we need to write data to in order to plot our pixel.

- 4) Use the remainder of (X/8) to look up in a table (below) the actual data to plot. The values corresponding to different remainders are as follows:

| Remainder (X/8) | Data to Write |

|-----------------|---------------|

| 0               | Hex 80        |

| 1               | Hex 40        |

| 2               | Hex 20        |

| 3               | Hex 10        |

| 4               | Hex 08        |

| 5               | Hex 04        |

| 6               | Hex 02        |

| 7               | Hex 01        |

The equation just described in the above paragraphs could be represented as follows:

BYTE ADDRESS = 8(INT(X/8)) + 256(INT(Y/8)) + R(Y/8)

WHERE R(Y/8) is equal to the remainder of (Y/8)

The actual data to write to the byte address is still obtained by taking the remainder of (X/8) and looking up the appropriate data value in the table.

# 8.4.2 Playing Games with VRAM Addressing

So far in Section 2.1 we have described how to use Graphics II Mode in its normal table-driven environment and how to arrange it as a bit-map. Now we are going to explain some other tricks you can play with the VDP. By experimenting with the values in VDP Registers R2 thru R6 (entering nonstandard initialization values), some interesting effects can be obtained.

You are forewarned that experimenting with VRAM addressing can cause some interesting effects but almost always produces some undesirable side effects such as losing the ability to use sprites or being only able to use a small number of sprites. Rather than dwell too long on this subject, we will describe one interesting new configuration that can be obtained and leave the rest to you.

Table 8-2 shows the register initialization values for the mode about to be described. Note that the only registers containing nonstandard values are Registers 3 and 4, which determine the Color Table and Pattern Table base address.

TABLE 8-2 -- NEW MODE INITIALIZATION VALUES

| REGISTER | MSBLSB   | HEX | DESCRIPTION                                          |

|----------|----------|-----|------------------------------------------------------|

| REG 0    | 00000010 | 02  | Graphics II Mode, No External Video                  |

| REG 1    | 11000010 | C2  | 16K,Enable Disp.,Disable Int.,16x16 Sprites,Mag.Off  |

| REG 2    | 00001110 | OE  | Address of Name Table in VRAM = Hex 3800             |

| REG 3    | 10011111 | 9F  | Color Table Address = Hex 2000 to Hex 2800           |

| REG 4    | 00000000 | 00  | Pattern Table Address = Hex 0000 to Hex 0800         |

| REG 5    | 01110110 | 76  | Address of Sprite Attribute Table in VRAM = Hex 3B00 |

| REG 6    | 00000011 | 03  | Address of Sprite Pattern Table in VRAM = 1800       |

| REG 7    | 00001111 | OF  | Backdrop Color = White                               |

What this mode does is effectively shrink the Graphics II Mode Color and Pattern Tables down from Hex 1800 bytes to Hex 800 bytes. This enables us to define up to 256 8x8 pixel patterns and 256 corresponding eight byte Color Table entries. Color is still mapped onto a pattern exactly as in Graphics II Mode.

The 768 byte Name Table is not split up into three equal sections as in Graphics II Mode but works as in Graphics I Mode. A byte of information written anywhere in the Name Table will select the appropriate pattern and the corresponding eight byte color entry and place it on the screen. In Appendix C can be found the Pattern Graphics Address Location Tables.

This mode is useful because it provides the memory savings of Graphics I Mode while allowing the color detail available in Graphics II Mode. However, a unique pattern for each screen position can no longer be defined, which is neccesary for highly detailed pictures or for bitmapping the screen. When in this mode 32 sprites can no longer be used. If you try to put more than eight sprites on the screen at once, they will start to duplicate themselves on the screen.

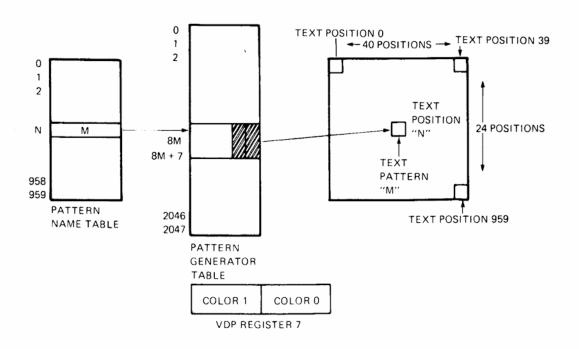

### 8.5 TEXT MODE

The VDP is in Text Mode when mode bits M1 = 1, M2 = 0, and M3 = 0. When in this mode the screen is divided up into 40 horizontal blocks by 24 vertical blocks, each of which may contain a character shape (see Figure 8-7.). Each of these character positions is six horizontal pixels by eight vertical pixels. There are only two tables required in VRAM in order to produce a Text Mode display, these are the Name Table and the Pattern Table. No Color Table is required in VRAM because the color of the character patterns is defined by the byte of information contained in VDP Register 7. The upper four bits define the color of all the bits on, and the lower four bits define the color of all the bits off. Therefore, if you had a value of Hex F1 written to Register 7, the text color would be white (F) while the background would be black (1).

FIGURE 8-7 — TEXT MODE NAME TABLE PATTERN POSITIONS

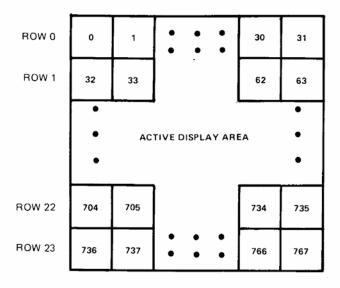

## 8.5.1 The Name Table

The Name Table in Text Mode is very similar to the one in Graphics I Mode except that the screen is now 40x24 instead of 32x24 (8x8 pixel blocks). This gives 960 screen positions and 960 (40x24 = 960) entries in our Name Table. Figure 8-8 shows the Name Table positions.

Each entry in the Name Table is one byte long and therefore can specify one of 255 (Hex FF) patterns. If the first entry in the Name Table is Hex 00, then the first pattern defined (Pattern 00) would be displayed in the upper left hand corner of the screen. If the first Name Table entry contains Hex FF, then the last pattern defined (Pattern FF) would be displayed in the upper left hand corner.

FIGURE 8-8 — PATTERN GRAPHICS NAME TABLE MAPPING

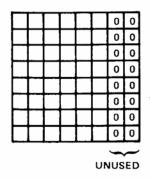

#### 8.5.2 The Pattern Table

The Pattern Table is 2048 (Hex 800) bytes long and is composed of 256 eight-byte patterns, each of which may represent a text or graphics character. Since each screen position is only six pixels across by eight pixels down instead of eight pixels across and eight pixels down as in the graphics modes, the VDP ignores the two least significant bits of each pattern. Therefore, in Text Mode a pattern is defined as show in Figure 8-9, leaving the two LSBs set to 0s and defining our character within the remaining 6x8 pixel block.

In order to leave a space between characters on the screen, most of the patterns defined for Text Mode will only use a 5x7 grid. Special graphics characters might be defined for drawing lines, graphs, and charts that use the entire 6x8 pixel grid area. A special character set for Graphics I Mode and Graphics II Mode is included in Appendix F.

FIGURE 8-9 — 6X8 PIXEL PATTERN GRID FOR TEXT MODE

Up to 256 different patterns can be defined in the Pattern Table, though less space is required if not all 256 patterns are required. For example, if your application only required numbers 0 through 9 and upper case A through Z to be defined, then only the first 36 patterns (288 bytes) would be needed. These 36 patterns would then be selected by writing numbers ranging from 0 to 36 (Hex 24) to bytes in the Name Table. If, for instance, the letter "A" was the first pattern defined, it could be placed in every possible screen position by writing a zero to all 960 Name Table entries.

Figure 8-10 illustrates how VRAM is mapped to the Pattern Plane in Text Mode.

FIGURE 8-10 — MAPPING OF VRAM INTO THE PATTERN PLANE IN TEXT MODE

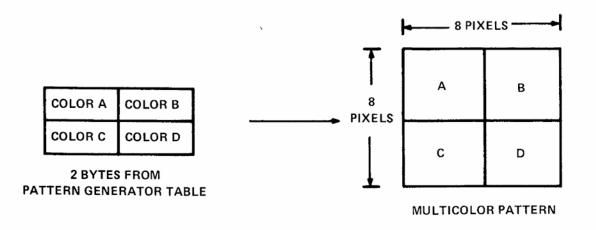

### 8.6 MULTICOLOR MODE

The VDP is in Multicolor Mode when the mode bits located in Registers 0 and 1 are equal to the following:

M1 = 0

M2 = 1

M3 = 0

Multicolor Mode provides a low-resolution display of 64 horizontal x 48 vertical color blocks. Each color block is equal to a 4x4 group of pixels and may be any of the sixteen VDP colors including transparent. The Backdrop color and Sprite Planes are also active in Multicolor Mode.

### NOTE

Multicolor Mode is not supported by the Texas Instruments Advanced Video Display Processor.

Only two tables are required in VRAM in order to produce a Multicolor Mode picture, these being the Name Table and the Pattern Table. The Name Table consists of 768 entries like the other graphics modes, although the Name Table no longer points to a color list because the color of the blocks is derived from the Pattern Table. The name points to an eight-byte segment of VRAM in the Pattern Table.

Only two bytes of the eight-byte segment area are used to specify the screen image. These two bytes specify four colors, each occupying a 4x4 pixel area. The four MSBs of the first byte define the color of the upper left hand corner of the multicolor pattern. The LSBs define the color of the upper right quarter. The second byte similarly defines the lower left and right quarters of the multicolor pattern. The two bytes thus map into an 8x8 pixel multicolor pattern as shown in Figure 8-11.

FIGURE 8-11 — MAPPING AN 8X8 PIXEL MULTICOLOR PATTERN

The location of the two bytes within the eight-byte segment pointed to by the name is dependent on the screen position where the name is mapped. For names in the top row (0-31), the two bytes are the first two in the eight-byte segments pointed to by the names. The next row of names (32-63) uses bytes number 3 and 4 within the eight-byte segment. The next row of names uses the 5th and 6th bytes, while the last row of names uses bytes 7 and 8. This series repeats for the remainder of the screen.

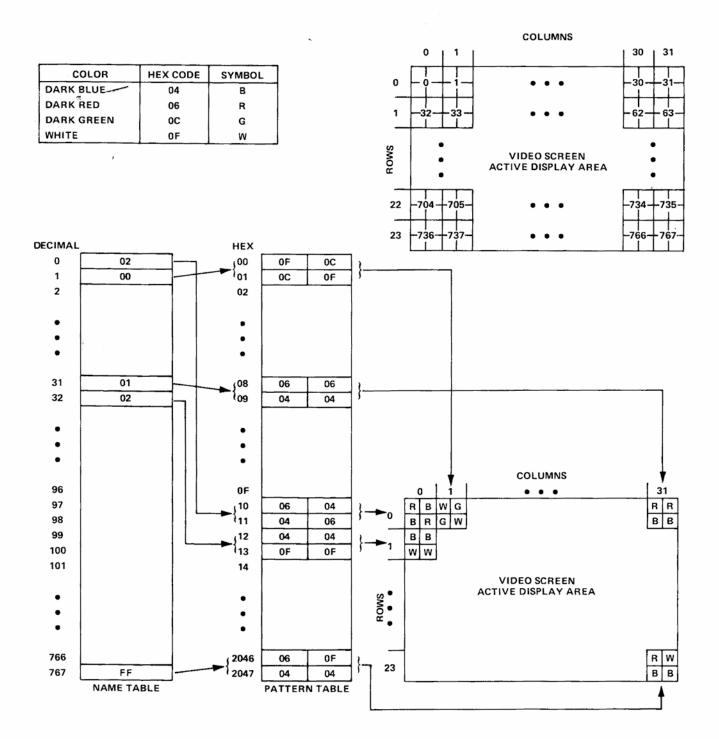

Let's go through a step-by-step example to help clear up any uncertainties about how Multicolor Mode works. Figure 8-12 is composed of a Multicolor Mode Name Table, Pattern Table, and a corresponding screen representation. Another screen image is also included to depict how the 767 screen positions, each composed of four 4x4 pixel blocks, fill the screen.

In our example (see Figure 8-12), a Name Table entry of Hex 02 points to locations Hex 08 and Hex 09. The first nibble of location Hex 08 contains the color red (Hex 06) and the second nibble contains the color blue (Hex 04). The first and second nibbles of the second byte contain blue and red, respectively. Therefore, screen position 0 contains the four colors specified. The calculations for this example and the others shown in Figure 8-12 are as follows.

### **EQUATION FOR FINDING PATTERN TABLE LOCATIONS**

FIRST BYTE = 2 \* ROW + NAME \* 8

SECOND BYTE = FIRST BYTE + 1

ROW = MOD4[TRUNCATE(PATTERN POSITION/32)]

# **CALCULATIONS FOR EXAMPLES SHOWN IN FIGURE 8-12**

| NAME<br>POSITION | PATTERN<br>NAME | PATTERN TABLE ROWS                                         |

|------------------|-----------------|------------------------------------------------------------|

| 0                | 02              | 2 * 0 + 02 * 8 = >10 (Byte 1)<br>10 + 1 = >11 (Byte 2)     |

| 1                | 00              | 2 * 0 + 00 * 8 = >00 (Byte 1)<br>00 + 1 = >01 (Byte 2)     |

| 31               | 01              | 2 * 0 + 01 * 8 = >08 (Byte 1)<br>08 + 1 = >09 (Byte 2)     |

| 32               | 02              | 2 * 1 + 02 * 8 = >12 (Byte 1)<br>12 + 1 = >13 (Byte 2)     |

| 767              | FF              | 2 * 3 + FF * 8 = >7FE (Byte 1)<br>01 + 7F8 = >7FF (Byte 2) |

FIGURE 8-12 — MULTICOLOR MAPPING SCHEME

The mapping of VRAM contents to screen image is simplified by using duplicate names in the Name Table since the series of bytes used within the eight-byte segment specifies a 2x8 pixel color square pattern on the screen as a straightforward translation from the eight-byte segment in VRAM pointed to by the common name.

When used in this manner, 768 bytes are still used for the Name Table and 1536 bytes are used for the color information in the Pattern Table (24 rows x 32 columns x 2-bytes/pattern position). Thus a total of 1728 bytes (6144  $\pm$  768) in VRAM are required. It should be noted that the tables begin on 1K and 2K boundries and are therefore not contiguous.

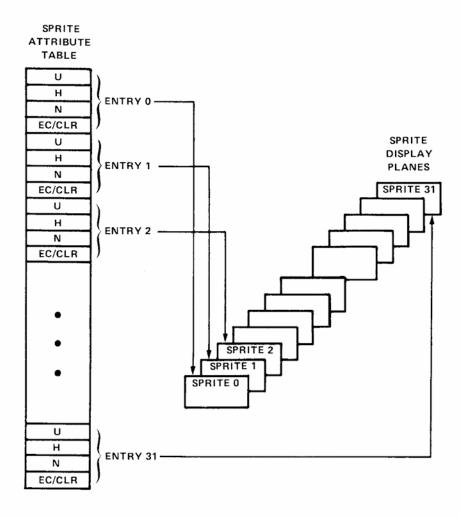

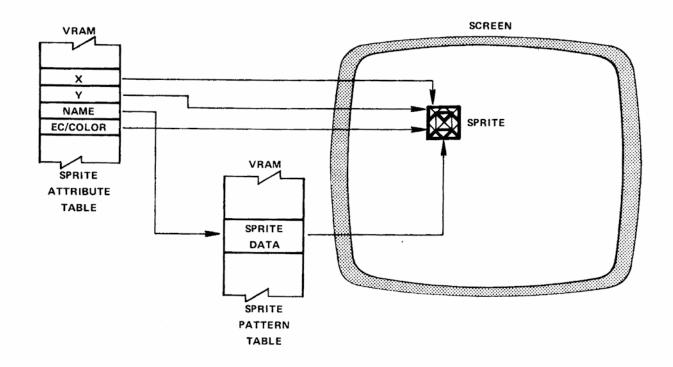

# SPRITES

Sprites are special animation-oriented patterns that can be made to move rapidly about the screen and change shape with very little programming effort. The video display has 32 Sprite Planes each of which contain a single sprite. These 32 Sprite Planes are numbered from 0 to 31 (see Section 2.1) with 0 being the highest priority or outermost Sprite Plane and 31 being the lowest priority Sprite Plane. When more than one sprite is located at the same screen coordinate the sprite on the higher priority plane will show through at that point. It should also be noted that all 32 sprites have a higher priority than the Pattern Plane and the Backdrop Plane.

Sprites come in two sizes, 8x8 pixels or 16x16 pixels. The size of all sprites is determined by the size bit in VDP Register 1. Register 1 also contains a sprite magnify bit which, when set, expands a sprite to double its normal size. Thus 8x8 sprites become 16x16, and 16x16 sprites would become 32x32. Unfortunately, when a sprite is magnified, its resolution is cut in half because the VDP maps each single pixel into a 2x2 pixel area.

Sprite patterns are defined in individual 8x8 pixel blocks exactly as patterns in Text or the graphics modes are. A Size 0 sprite (8x8 pixels) would require only one pattern to be defined. A Size 1 sprite (16x16 pixels) is made up of four 8x8 pixel patterns. All of the bits on within a sprite pattern are a single color, which can be any one of the 16 available VDP colors. Any bits off within a sprite pattern are automatically set to the VDP color transparent, which allows the Pattern Plane or Backdrop color to show through at those points. Any area within a sprite display plane outside of the sprite itself is also set to transparent. A good way to visualize this is to imagine a Sprite Plane as a pane of glass on which you can stick a single 8x8 or 16x16 pixel object.

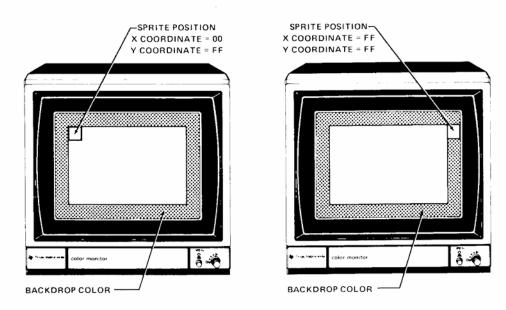

Two tables are required in VRAM in order to produce a sprite display. The Sprite Attribute Table tells us some characteristics of each sprite, like screen location, color, and what pattern to pick for the shape of the sprite. The Sprite Pattern Table contains a library of sprite shape data to choose from.

All 32 VDP sprites may be displayed on the screen at the same time, however, a maximum of four sprites may be displayed on one horizontal line. If this rule is violated, the four highest priority sprites will be displayed normally, while the fifth and subsequent sprites will be automatically set to transparent. Furthermore, the Fifth Sprite Flag in the VDP Status Register is set to a 1, and the number of the violating fifth sprite is loaded into the Status Register. See Section 5.2 for more information on fifth sprites and the Status Register.

The VDP also provides limited sprite coincidence checking. If any two active sprites have overlapping bits, then the Coincidence Flag in the VDP Status Register will be set to a 1. It should be noted that the VDP only tells you if any two sprites are coinciding and does not specify the numbers of the sprites that are overlapping. Most applications that require knowing which sprites are coinciding continually monitor the Sprite Attribute Table for overlapping values.

# 9.1 THE SPRITE PATTERN TABLE

The Sprite Pattern Table has a maximum length of 2048 (Hex 800) bytes and is located in VRAM beginning on a 2K byte boundry. Its actual location in VRAM is determined by the base address in VDP Register 6.

It takes eight bytes of information to define the pattern of a Size 0 (8x8 pixel) sprite and 32 bytes (8x4) of data to define the pattern of a Size 1 (16x16 pixel) sprite. Therefore, 256 patterns can be defined for Size 0 sprites or 64 patterns for Size 1 sprites.

The Sprite Pattern Table can be as short as eight bytes if Size 0 sprites are used and 32 bytes if Size 1 sprites are used because the same sprite shape can be reused for as many sprites as desired. To select the same sprite pattern just repeat the name byte located in the Sprite Attribute Table.

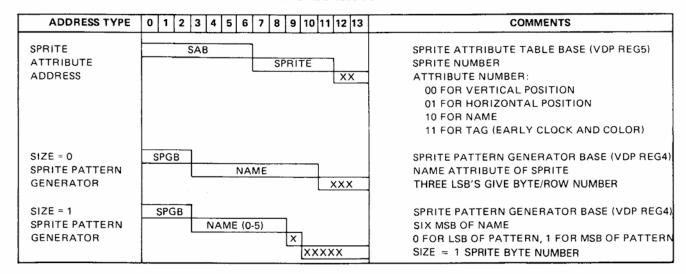

## 9.2 THE SPRITE ATTRIBUTE TABLE

The Sprite Attribute Table contains four bytes of information for every sprite displayed. If all 32 sprites are to be displayed, then the table would have a maximum length of 128 bytes. The location of the Attribute Table in VRAM is defined by the base address contained in VDP Register 5.

The first four byte entry in the Sprite Attribute Table contains information pertaining to Sprite 0, which is the highest priority sprite. The last four byte entry in the Sprite Attribute Table contains information for the lowest priority sprite, Sprite 31. Figure 9-1 illustrates how the Sprite Attribute Table relates to the Sprite Planes.

FIGURE 9-1 — SPRITE ATTRIBUTE TABLE AS RELATED TO SPRITE PLANES

Referring to Figure 9-2, let's examine one four byte attribute entry. The first two bytes determine the coordinate of the sprite on the display screen. The first byte is the vertical position and the second byte is the horizontal position. The third byte is the sprite name and specifies what pattern in the Sprite Pattern Table will be used as the sprite's shape. The fourth byte performs two functions: the lower four bits (nibble) determine the color of the sprite and the Early Clock bit (MSB) shifts the horizontal position of the sprite towards the left 32 pixels. Setting this bit high allows sprites to bleed (flow smoothly) off the left side of the screen. The other three bits in this fourth byte are unused and should be set to zeros.

|                            |                |        |        | BIT N  | UMBER  |        |        |        |        |

|----------------------------|----------------|--------|--------|--------|--------|--------|--------|--------|--------|

|                            | MSB            |        |        |        |        |        |        | LSB    |        |

|                            | 0              | 11     | 2      | 3      | 4      | 5      | 6      | 7      |        |

| VERTICAL COORDINATE        | VERT.          | VERT.  | VERT.  | VERT.  | VERT.  | VERT.  | VERT.  | VERT.  | BYTEO  |

| VENTICAL COORDINATE        | POSN.          | POSN.  | POSN.  | POSN.  | POSN.  | POSN.  | POSN.  | POSN.  | LBITEO |

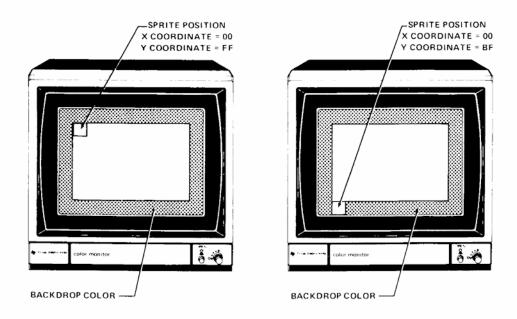

| HORIZONTAL COORDINATE      | HORIZ.         | HORIZ. | HORIZ. | HORIZ. | HORIZ. | HORIZ. | HORIZ. | HORIZ. | BYTE 1 |