mirror of

https://github.com/freitz85/AppleIISd.git

synced 2025-04-02 17:31:58 +00:00

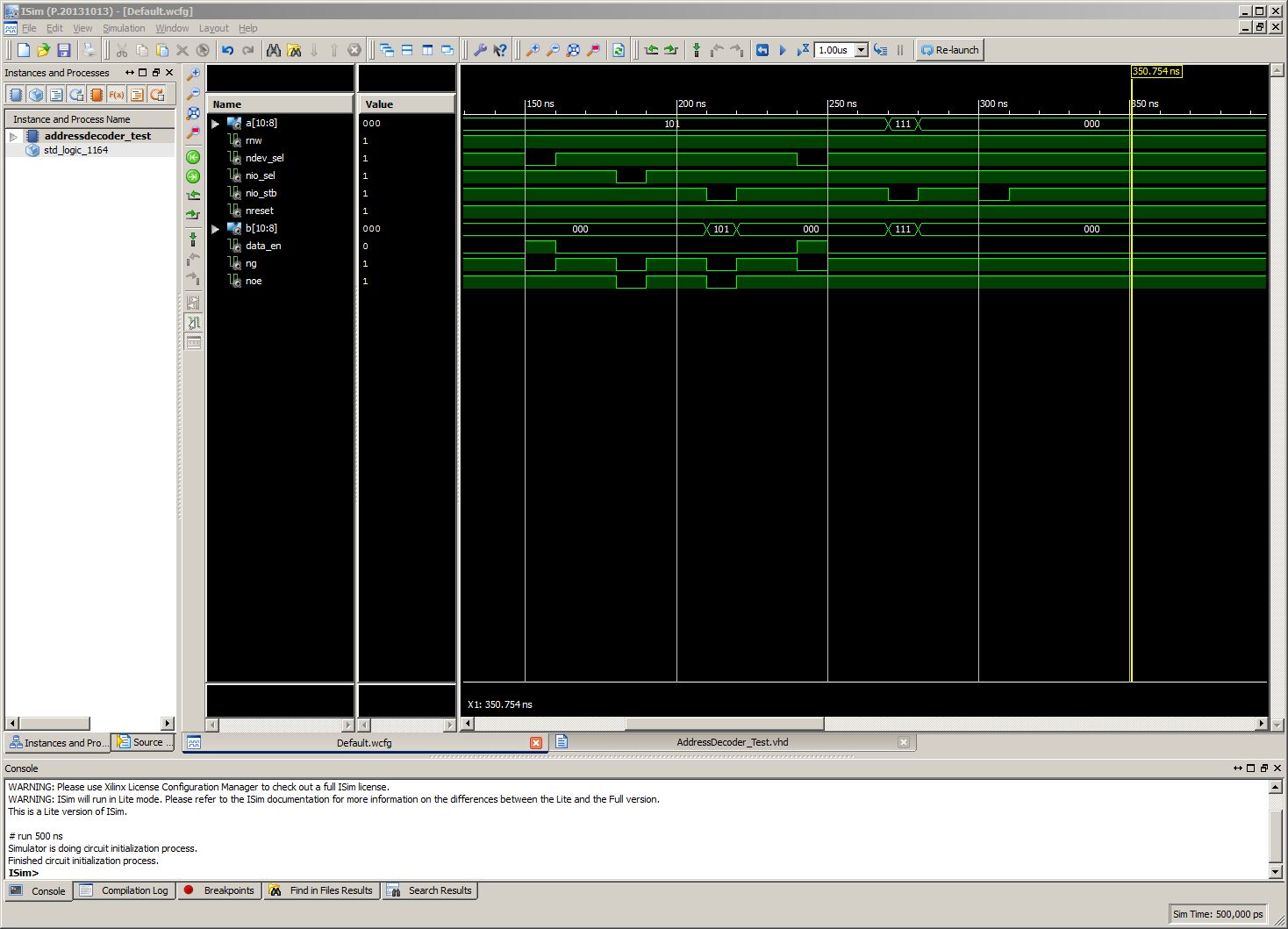

AddressDecoder testbench

This commit is contained in:

parent

819904bea2

commit

eeb0b14725

BIN

Images/AddessDecoder_Test.JPG

Normal file

BIN

Images/AddessDecoder_Test.JPG

Normal file

Binary file not shown.

|

After

(image error) Size: 189 KiB |

BIN

Images/AppleIISd_Test.JPG

Normal file

BIN

Images/AppleIISd_Test.JPG

Normal file

Binary file not shown.

|

After

(image error) Size: 280 KiB |

@ -54,7 +54,9 @@ begin

|

||||

DATA_EN <= RNW and not NDEV_SEL;

|

||||

NG <= NDEV_SEL and noe_int;

|

||||

NOE <= noe_int;

|

||||

noe_int <= not RNW or not NDEV_SEL or NIO_STB or ncs;

|

||||

noe_int <= not RNW or not NDEV_SEL

|

||||

or (NIO_SEL and NIO_STB)

|

||||

or (NIO_SEL and ncs);

|

||||

|

||||

cfxx <= A(8) and A(9) and A(10) and not NIO_STB;

|

||||

|

||||

|

||||

@ -1,79 +1,136 @@

|

||||

-- Vhdl test bench created from schematic U:\AppleIISd\VHDL\AddressDecoder.sch - Mon Oct 09 20:12:16 2017

|

||||

--------------------------------------------------------------------------------

|

||||

-- Company:

|

||||

-- Engineer:

|

||||

--

|

||||

-- Create Date: 23:42:22 10/10/2017

|

||||

-- Design Name:

|

||||

-- Module Name: C:/Git/AppleIISd/VHDL/AddressDecoder_Test.vhd

|

||||

-- Project Name: AppleIISd

|

||||

-- Target Device:

|

||||

-- Tool versions:

|

||||

-- Description:

|

||||

--

|

||||

-- VHDL Test Bench Created by ISE for module: AddressDecoder

|

||||

--

|

||||

-- Dependencies:

|

||||

--

|

||||

-- Revision:

|

||||

-- Revision 0.01 - File Created

|

||||

-- Additional Comments:

|

||||

--

|

||||

-- Notes:

|

||||

-- 1) This testbench template has been automatically generated using types

|

||||

-- std_logic and std_logic_vector for the ports of the unit under test.

|

||||

-- Xilinx recommends that these types always be used for the top-level

|

||||

-- I/O of a design in order to guarantee that the testbench will bind

|

||||

-- correctly to the timing (post-route) simulation model.

|

||||

-- 2) To use this template as your testbench, change the filename to any

|

||||

-- name of your choice with the extension .vhd, and use the "Source->Add"

|

||||

-- menu in Project Navigator to import the testbench. Then

|

||||

-- edit the user defined section below, adding code to generate the

|

||||

-- stimulus for your design.

|

||||

--

|

||||

-- This testbench has been automatically generated using types std_logic and

|

||||

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

|

||||

-- that these types always be used for the top-level I/O of a design in order

|

||||

-- to guarantee that the testbench will bind correctly to the post-implementation

|

||||

-- simulation model.

|

||||

--------------------------------------------------------------------------------

|

||||

LIBRARY ieee;

|

||||

USE ieee.std_logic_1164.ALL;

|

||||

USE ieee.numeric_std.ALL;

|

||||

LIBRARY UNISIM;

|

||||

USE UNISIM.Vcomponents.ALL;

|

||||

ENTITY AddressDecoder_AddressDecoder_sch_tb IS

|

||||

END AddressDecoder_AddressDecoder_sch_tb;

|

||||

ARCHITECTURE behavioral OF AddressDecoder_AddressDecoder_sch_tb IS

|

||||

|

||||

-- Uncomment the following library declaration if using

|

||||

-- arithmetic functions with Signed or Unsigned values

|

||||

--USE ieee.numeric_std.ALL;

|

||||

|

||||

ENTITY AddressDecoder_Test IS

|

||||

END AddressDecoder_Test;

|

||||

|

||||

ARCHITECTURE behavior OF AddressDecoder_Test IS

|

||||

|

||||

-- Component Declaration for the Unit Under Test (UUT)

|

||||

|

||||

COMPONENT AddressDecoder

|

||||

PORT(

|

||||

A : IN std_logic_vector(10 downto 8);

|

||||

B : OUT std_logic_vector(10 downto 8);

|

||||

RNW : IN std_logic;

|

||||

NDEV_SEL : IN std_logic;

|

||||

NIO_SEL : IN std_logic;

|

||||

NIO_STB : IN std_logic;

|

||||

NRESET : IN std_logic;

|

||||

DATA_EN : OUT std_logic;

|

||||

NG : OUT std_logic;

|

||||

NOE : OUT std_logic

|

||||

);

|

||||

END COMPONENT;

|

||||

|

||||

|

||||

COMPONENT AddressDecoder

|

||||

PORT( A10 : IN STD_LOGIC;

|

||||

A9 : IN STD_LOGIC;

|

||||

A8 : IN STD_LOGIC;

|

||||

B10 : OUT STD_LOGIC;

|

||||

B9 : OUT STD_LOGIC;

|

||||

B8 : OUT STD_LOGIC;

|

||||

NIO_SEL : IN STD_LOGIC;

|

||||

NDEV_SEL : IN STD_LOGIC;

|

||||

NOE : OUT STD_LOGIC;

|

||||

RNW : IN STD_LOGIC;

|

||||

NG : OUT STD_LOGIC;

|

||||

DATA_EN : OUT STD_LOGIC;

|

||||

NIO_STB : IN STD_LOGIC);

|

||||

END COMPONENT;

|

||||

|

||||

SIGNAL A10 : STD_LOGIC := '0';

|

||||

SIGNAL A9 : STD_LOGIC := '0';

|

||||

SIGNAL A8 : STD_LOGIC := '0';

|

||||

SIGNAL B10 : STD_LOGIC;

|

||||

SIGNAL B9 : STD_LOGIC;

|

||||

SIGNAL B8 : STD_LOGIC;

|

||||

SIGNAL NIO_SEL : STD_LOGIC := '1';

|

||||

SIGNAL NDEV_SEL : STD_LOGIC := '1';

|

||||

SIGNAL NOE : STD_LOGIC;

|

||||

SIGNAL RNW : STD_LOGIC := '1';

|

||||

SIGNAL NG : STD_LOGIC;

|

||||

SIGNAL DATA_EN : STD_LOGIC;

|

||||

SIGNAL NIO_STB : STD_LOGIC := '1';

|

||||

--Inputs

|

||||

signal A : std_logic_vector(10 downto 8) := "101";

|

||||

signal RNW : std_logic := '1';

|

||||

signal NDEV_SEL : std_logic := '1';

|

||||

signal NIO_SEL : std_logic := '1';

|

||||

signal NIO_STB : std_logic := '1';

|

||||

signal NRESET : std_logic := '1';

|

||||

|

||||

--Outputs

|

||||

signal B : std_logic_vector(10 downto 8);

|

||||

signal DATA_EN : std_logic;

|

||||

signal NG : std_logic;

|

||||

signal NOE : std_logic;

|

||||

|

||||

BEGIN

|

||||

|

||||

-- Instantiate the Unit Under Test (UUT)

|

||||

uut: AddressDecoder PORT MAP (

|

||||

A => A,

|

||||

B => B,

|

||||

RNW => RNW,

|

||||

NDEV_SEL => NDEV_SEL,

|

||||

NIO_SEL => NIO_SEL,

|

||||

NIO_STB => NIO_STB,

|

||||

NRESET => NRESET,

|

||||

DATA_EN => DATA_EN,

|

||||

NG => NG,

|

||||

NOE => NOE

|

||||

);

|

||||

|

||||

|

||||

UUT: AddressDecoder PORT MAP(

|

||||

A10 => A10,

|

||||

A9 => A9,

|

||||

A8 => A8,

|

||||

B10 => B10,

|

||||

B9 => B9,

|

||||

B8 => B8,

|

||||

NIO_SEL => NIO_SEL,

|

||||

NDEV_SEL => NDEV_SEL,

|

||||

NOE => NOE,

|

||||

RNW => RNW,

|

||||

NG => NG,

|

||||

DATA_EN => DATA_EN,

|

||||

NIO_STB => NIO_STB

|

||||

);

|

||||

-- Stimulus process

|

||||

stim_proc: process

|

||||

begin

|

||||

-- hold reset state for 100 ns.

|

||||

wait for 50 ns;

|

||||

NRESET <= '0';

|

||||

wait for 50 ns;

|

||||

NRESET <= '1';

|

||||

wait for 50 ns;

|

||||

|

||||

-- *** Test Bench - User Defined Section ***

|

||||

tb : PROCESS

|

||||

BEGIN

|

||||

WAIT; -- will wait forever

|

||||

END PROCESS;

|

||||

-- *** End Test Bench - User Defined Section ***

|

||||

-- insert stimulus here

|

||||

-- CPLD access

|

||||

NDEV_SEL <= '0';

|

||||

wait for 10 ns;

|

||||

NDEV_SEL <= '1';

|

||||

wait for 20 ns;

|

||||

-- CnXX access

|

||||

NIO_SEL <= '0';

|

||||

wait for 10 ns;

|

||||

NIO_SEL <= '1';

|

||||

wait for 20 ns;

|

||||

-- C8xx access, selected

|

||||

NIO_STB <= '0';

|

||||

wait for 10 ns;

|

||||

NIO_STB <= '1';

|

||||

wait for 20 ns;

|

||||

-- CPLD access

|

||||

NDEV_SEL <= '0';

|

||||

wait for 10 ns;

|

||||

NDEV_SEL <= '1';

|

||||

wait for 20 ns;

|

||||

-- CFFF access

|

||||

A <= "111";

|

||||

NIO_STB <= '0';

|

||||

wait for 10 ns;

|

||||

A <= "000";

|

||||

NIO_STB <= '1';

|

||||

wait for 20 ns;

|

||||

-- C8xx access, unselected

|

||||

NIO_STB <= '0';

|

||||

wait for 10 ns;

|

||||

NIO_STB <= '1';

|

||||

wait for 20 ns;

|

||||

|

||||

wait;

|

||||

end process;

|

||||

|

||||

END;

|

||||

|

||||

Binary file not shown.

1058

VHDL/AppleIISd.jed

1058

VHDL/AppleIISd.jed

File diff suppressed because it is too large

Load Diff

@ -72,6 +72,7 @@ architecture Behavioral of AppleIISd is

|

||||

|

||||

signal rnw_int : std_logic;

|

||||

signal data_en : std_logic;

|

||||

signal ndev_sel_int : std_logic;

|

||||

|

||||

component SpiController is

|

||||

Port (

|

||||

@ -131,7 +132,7 @@ begin

|

||||

A => ADD_HIGH,

|

||||

B => B,

|

||||

RNW => RNW,

|

||||

NDEV_SEL => NDEV_SEL,

|

||||

NDEV_SEL => ndev_sel_int,

|

||||

NIO_SEL => NIO_SEL,

|

||||

NIO_STB => NIO_STB,

|

||||

NRESET => NRESET,

|

||||

@ -155,6 +156,15 @@ begin

|

||||

end if;

|

||||

end process;

|

||||

|

||||

process(CLK, NRESET)

|

||||

begin

|

||||

if(NRESET = '0') then

|

||||

ndev_sel_int <= '1';

|

||||

elsif rising_edge(CLK) then

|

||||

ndev_sel_int <= NDEV_SEL;

|

||||

end if;

|

||||

end process;

|

||||

|

||||

DATA <= data_out when (data_en = '1') else (others => 'Z'); -- data bus tristate

|

||||

|

||||

-- synthesis translate_off

|

||||

|

||||

@ -34,6 +34,10 @@

|

||||

<association xil_pn:name="BehavioralSimulation" xil_pn:seqID="2"/>

|

||||

<association xil_pn:name="Implementation" xil_pn:seqID="2"/>

|

||||

</file>

|

||||

<file xil_pn:name="AddressDecoder_Test.vhd" xil_pn:type="FILE_VHDL">

|

||||

<association xil_pn:name="BehavioralSimulation" xil_pn:seqID="0"/>

|

||||

<association xil_pn:name="PostRouteSimulation" xil_pn:seqID="230"/>

|

||||

</file>

|

||||

</files>

|

||||

|

||||

<properties>

|

||||

|

||||

Loading…

x

Reference in New Issue

Block a user